# Components

This catalogue is intended for electronic engineers involved in the design of telephony equipment. It includes only those components likely to be of direct interest. When selecting a component supplier Philips is the natural choice. We are backed by worldwide research resources, plus development, application and quality laboratories. Our in depth knowledge, our command of proven technologies and our unequalled mass-production experience, plus our firm commitment to meeting the needs of the industrial and professional sectors, mean that when dealing with us, you deal with a partner, not just a supplier.

Recognizing the specific needs of the telephony industry, we are well aware of the need for an intensive dialogue between equipment and component manufacturers. Detecting and keeping pace with system trends is a prerequisite to the development of new, advanced components. Components that will be required to provide a system life of 25 to 30 years.

If you are seeking such a dialogue, contact Philips, the company with the broadest technological base in the industry, and the one with a proven record in innovation, in high quality and in high volume production.

## SUBSCRIBER

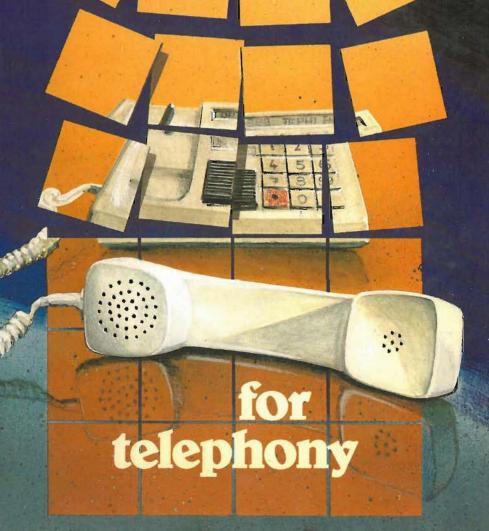

Revolutionary changes in subscriber-set design have greatly increased the scope and quality of the services offered. We offer many components for this and the next generation of subscriber equipment. Noteworthy are ICs for line current interrupt dialling or two-tone dialling, ringing, speech/transmission ICs, and a special microcomputer with peripherals such as two-tone diallers, RAM and LCD

For the future Integrated Services

Digital Network, we have some

special ICs in development –

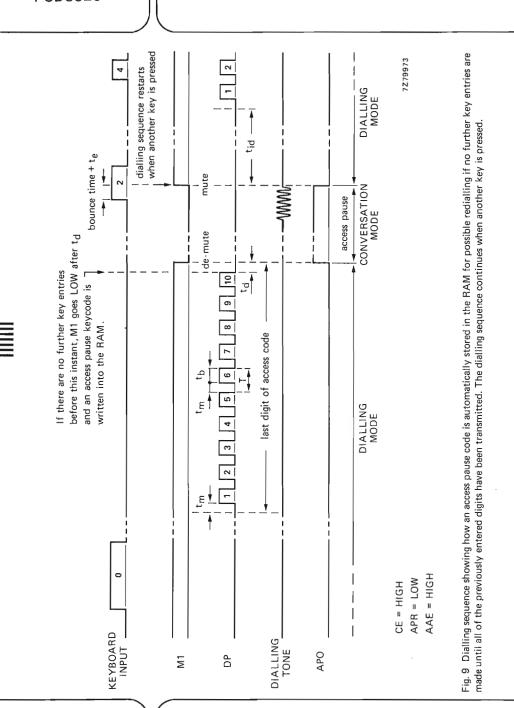

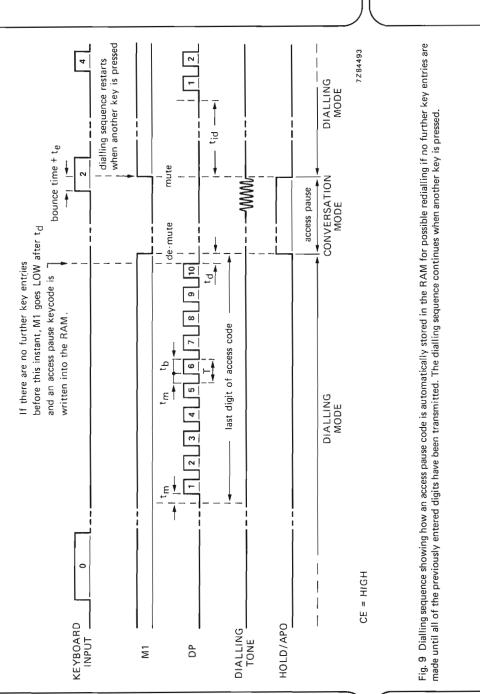

particularly for the digital

subscriber set.

Besides ICs we offer dedicated

components for over-voltage

protection, quartz crystals, some

special MOSFETs, loudspeakers and

a complete LCD module.

drivers.

# **Contents**

| SURVEY                                                                                                                                                                                                              | 4                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DEDICATED INTEGRATED CIRCUITS FOR TELEPHONE SUBSCRIBER SETS                                                                                                                                                         | 6                                      |

| Introduction                                                                                                                                                                                                        | 6                                      |

| Architecture of electronic subscriber sets                                                                                                                                                                          | 7                                      |

| Comparisons                                                                                                                                                                                                         | 10                                     |

| Bipolar ICs for telephone<br>subscriber sets<br>DTMF diallers with line<br>interface<br>Speech/transmission<br>circuits<br>DTMF/speech/trans-                                                                       | 13<br>15<br>47                         |

| mission combination<br>Miscellaneous bipolar ICs                                                                                                                                                                    | 121<br>139                             |

| CMOS ICs for telephone subscriber sets Pulse diallers with redial Pulse repertory dialler/ telephone-set controller Microcomputer peripherals (DTMF/MODEM, RAM, LCD, clock) Multi-tone ringer 4-digit clock circuit | 153<br>155<br>269<br>293<br>323<br>327 |

| OTHER COMPONENTS<br>FOR TELEPHONE<br>SUBSCRIBER SETS                                                                                                                                                                | 337                                    |

| Protection of telephone sets Miscellaneous                                                                                                                                                                          | 339<br>355                             |

| OTHER COMPONENTS<br>FOR TELEPHONY                                                                                                                                                                                   | 389                                    |

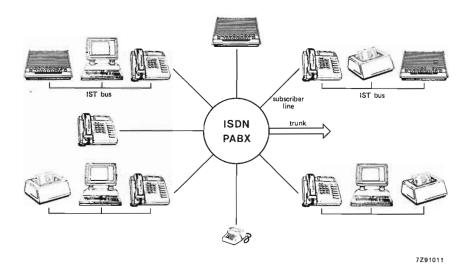

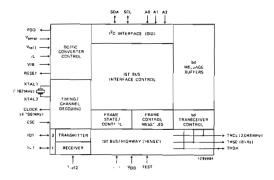

| ISDN-kit<br>IST-bus interface circuit                                                                                                                                                                               | 391<br>395                             |

# SURVEY

| type no.                                                       | function                                                                                                                                                                      | status                                                                                      | page                                                        |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| ВІРС                                                           | CLAR INTEGRATED CIRCUITS FOR TELEPHONI                                                                                                                                        | E SUBSCRIBER SETS                                                                           |                                                             |

| TDA 1077                                                       | DTMF generator for telephone dialling                                                                                                                                         | production                                                                                  | 17                                                          |

| TEA1021                                                        | idem                                                                                                                                                                          | production                                                                                  | 23                                                          |

| TEA1043                                                        | idem                                                                                                                                                                          | production                                                                                  | 31                                                          |

| TEA1044                                                        | idem                                                                                                                                                                          | production                                                                                  | 39                                                          |

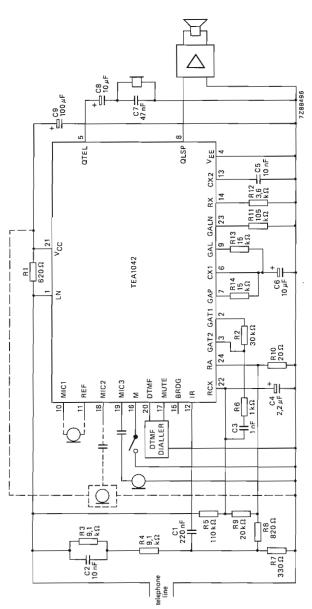

| TEA1042                                                        | telephone transmission circuit                                                                                                                                                | production                                                                                  | 49                                                          |

| TEA1053                                                        | idem                                                                                                                                                                          | production                                                                                  | 65                                                          |

| TEA1054                                                        | idem                                                                                                                                                                          | production                                                                                  | 65                                                          |

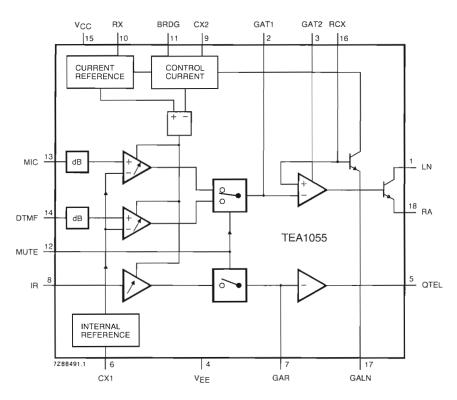

| TEA1055                                                        | idem                                                                                                                                                                          | production                                                                                  | 79                                                          |

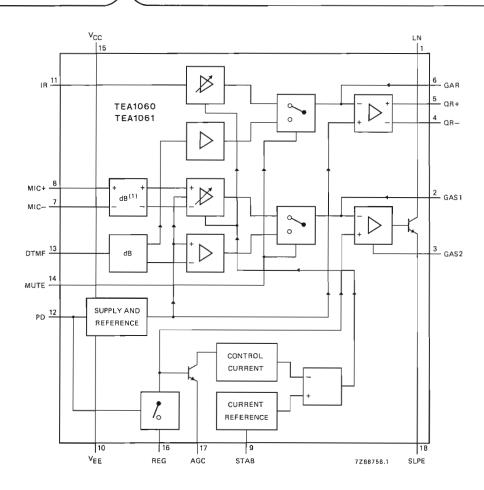

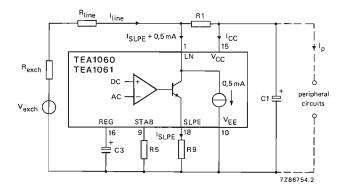

| TEA1060                                                        | idem                                                                                                                                                                          | development                                                                                 | 93                                                          |

| TEA1061                                                        | idem                                                                                                                                                                          | development                                                                                 | 93                                                          |

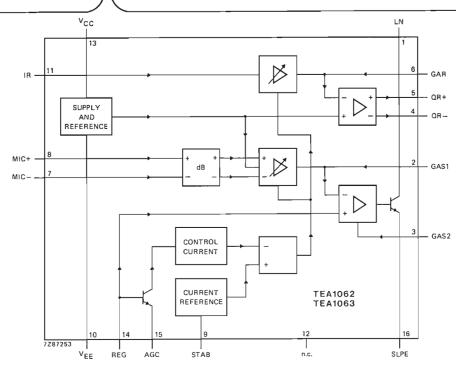

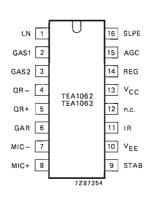

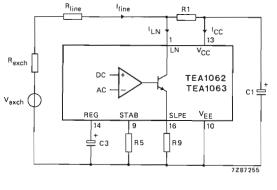

| TEA1062                                                        | idem                                                                                                                                                                          | development                                                                                 | 109                                                         |

| TEA1063                                                        | idem                                                                                                                                                                          | development                                                                                 | 109                                                         |

| TEA1046                                                        | DTMF/speech/transmission combination                                                                                                                                          | samples                                                                                     | 123                                                         |

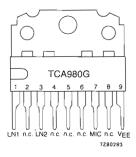

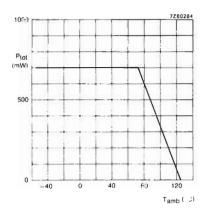

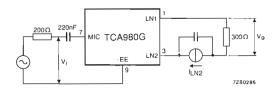

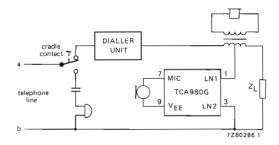

| TCA980G                                                        | microphone amplifier                                                                                                                                                          | production                                                                                  | 141                                                         |

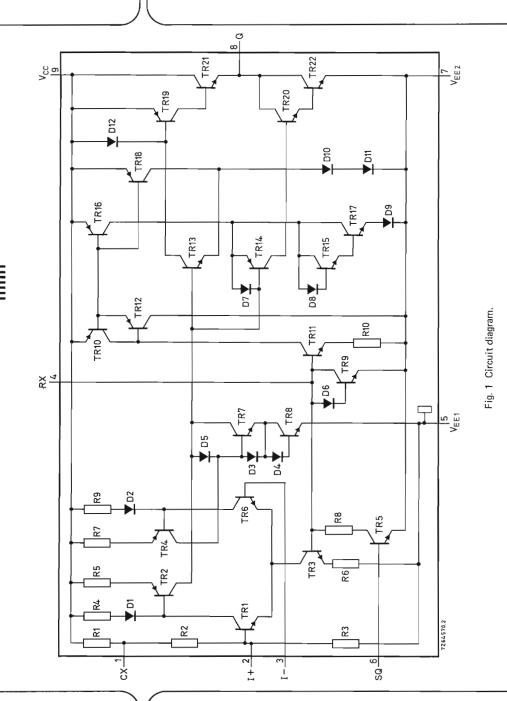

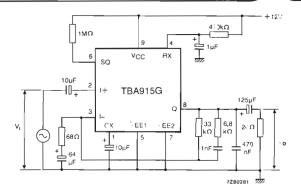

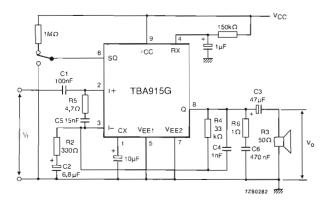

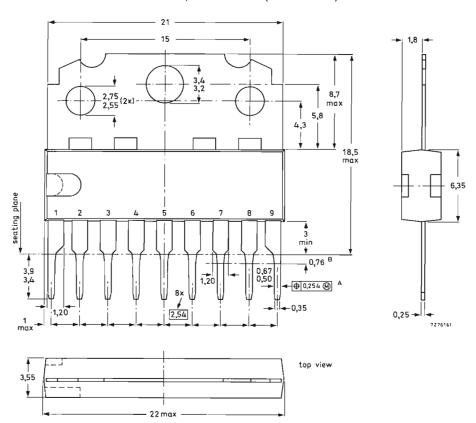

| TBA915G                                                        | audio amplifier                                                                                                                                                               | production                                                                                  | 147                                                         |

| СМ                                                             | OS INTEGRATED CIRCUITS FOR TELEPHONE S                                                                                                                                        | SUBSCRIBER SETS                                                                             |                                                             |

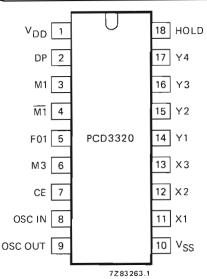

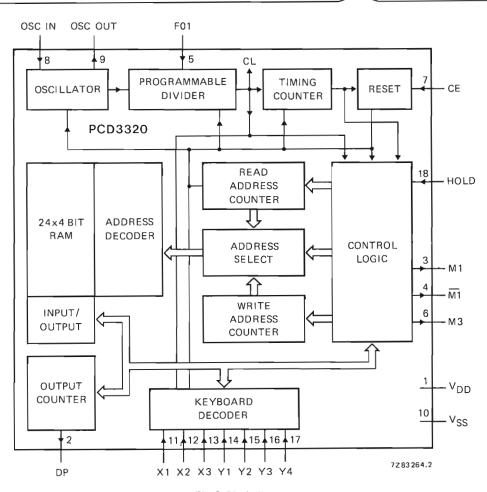

| PCD3320                                                        | interrupted current-loop dialling circuit                                                                                                                                     | production                                                                                  | 157                                                         |

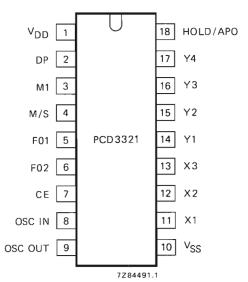

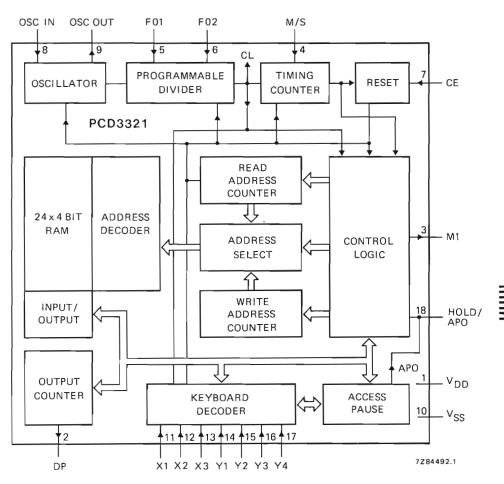

| PCD3321                                                        | idem                                                                                                                                                                          | production                                                                                  | 173                                                         |

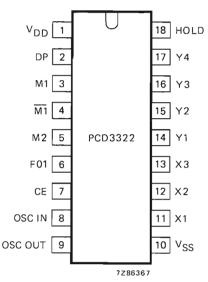

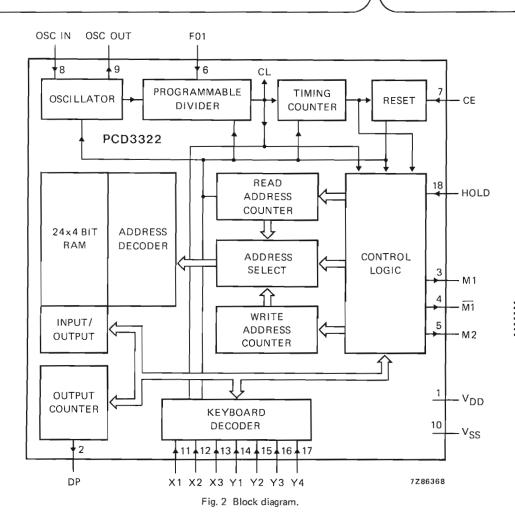

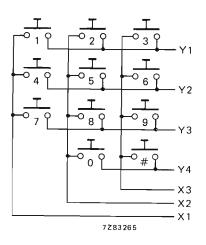

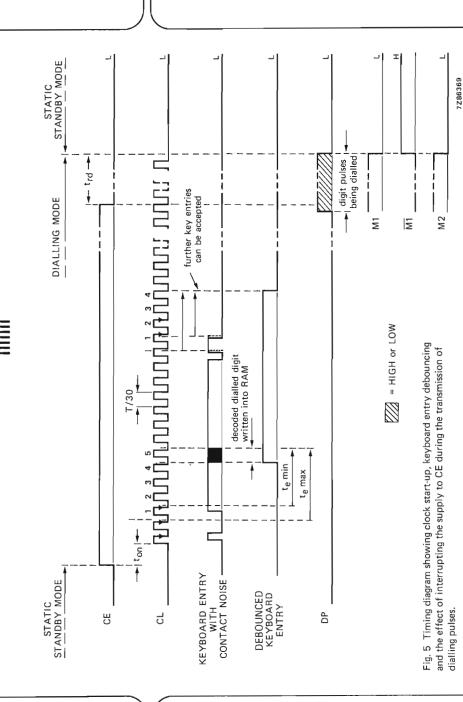

| PCD3322                                                        | idem                                                                                                                                                                          | production                                                                                  | 191                                                         |

| PCD3323                                                        |                                                                                                                                                                               |                                                                                             |                                                             |

|                                                                | idem                                                                                                                                                                          | production                                                                                  | 207                                                         |

| PCD3324                                                        | idem                                                                                                                                                                          | production                                                                                  | 207<br>231                                                  |

| PCD3325                                                        | idem<br>idem                                                                                                                                                                  | production production                                                                       | 207<br>231<br>251                                           |

| PCD3325                                                        | idem                                                                                                                                                                          | production                                                                                  | 207<br>231                                                  |

|                                                                | idem<br>idem<br>pulse repertory dialler/telephone set                                                                                                                         | production production                                                                       | 207<br>231<br>251                                           |

| PCD3325<br>PCD3341<br>PCD3311                                  | idem idem pulse repertory dialler/telephone set controller microcomputer peripheral                                                                                           | production<br>production<br>development                                                     | 207<br>231<br>251<br>271                                    |

| PCD3325<br>PCD3341<br>PCD3311<br>PCD3312                       | idem idem pulse repertory dialler/telephone set controller microcomputer peripheral DTMF generator/modem generator                                                            | production<br>production<br>development<br>development                                      | 207<br>231<br>251<br>271<br>275                             |

| PCD3325<br>PCD3341<br>PCD3311<br>PCD3312<br>PCD8571            | idem idem pulse repertory dialler/telephone set controller microcomputer peripheral DTMF generator/modem generator idem                                                       | production<br>production<br>development<br>development<br>development                       | 207<br>231<br>251<br>271<br>275                             |

| PCD3325<br>PCD3341<br>PCD3311<br>PCD3312<br>PCD8571<br>PCB8573 | idem idem pulse repertory dialler/telephone set controller microcomputer peripheral DTMF generator/modem generator idem 128 x 8 bit static RAM                                | production<br>production<br>development<br>development<br>development<br>samples            | 207<br>231<br>251<br>271<br>275<br>275<br>277               |

| PCD3325<br>PCD3341                                             | idem idem pulse repertory dialler/telephone set controller microcomputer peripheral DTMF generator/modem generator idem 128 x 8 bit static RAM clock/calendar with serial I/O | production<br>production<br>development<br>development<br>development<br>samples<br>samples | 207<br>231<br>251<br>271<br>275<br>275<br>277<br>279<br>291 |

| type no.                                                                                                 | function                                                                                                                                                                                                                        | status                                                                           | pag                                           |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|--|

| OTHER COMPONENTS FOR TELEPHONE SUBSCRIBER SETS                                                           |                                                                                                                                                                                                                                 |                                                                                  |                                               |  |  |  |  |

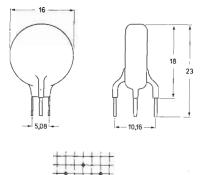

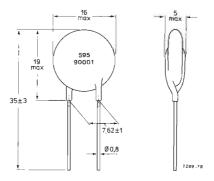

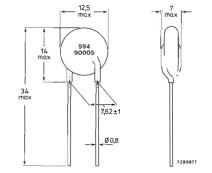

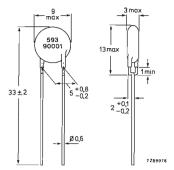

| 2322 593 90001<br>2322 594 90005<br>2322 594 90008<br>2322 594 90009<br>2322 595 90001<br>2322 599 91001 | VDR for protection (voltage > 90 V @ 1 mA) idem (voltage > 103 V @ 0,1 mA) idem (voltage > 68 V @ 0,01 mA) idem (voltage > 100 V @ 1 mA) idem (voltage > 130 V @ 1 mA) PVP module for mains protection (voltage > 135 V @ 1 mA) | production<br>production<br>production<br>production<br>production<br>production | 353<br>351<br>351<br>351<br>349<br>347        |  |  |  |  |

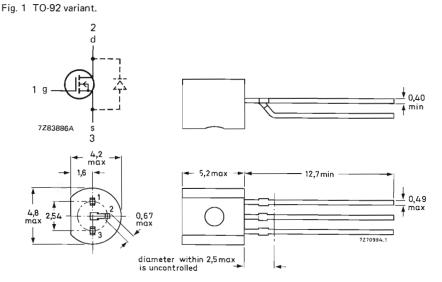

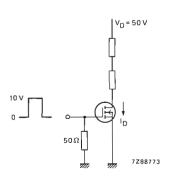

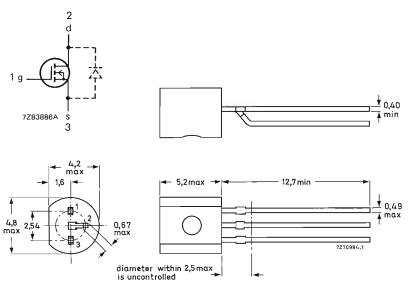

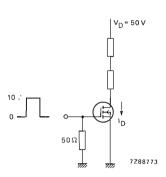

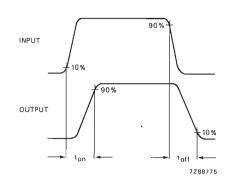

| 2322 599 91002<br>2322 670 90003<br>2322 672 98001<br>BZW14<br>BST72<br>BST74<br>BST76                   | idem (voltage > 180 V @ 1 mA) PTC thermistor (current stabiliser) idem transient suppressor diode DMOS transistor (100 V) idem (200 V) idem (200 V)                                                                             | samples production production development development development development    | 347<br>345<br>343<br>341<br>357<br>361<br>365 |  |  |  |  |

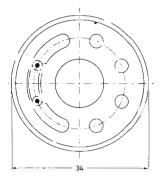

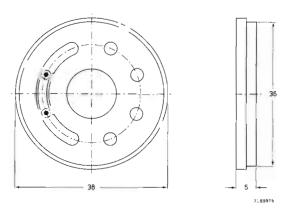

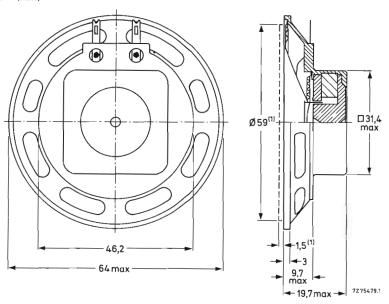

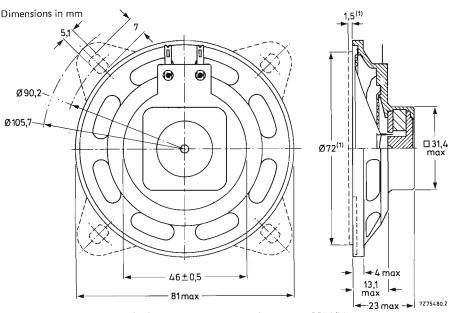

| AD01980/Z<br>AD01985/Z<br>AD2071/Z<br>AD3071/Y<br>AD3371/Y                                               | loudspeaker (1,5 inch) idem (1,5 inch) idem (2,5 inch) idem (3 inch) idem (3 inch) idem (3 inch)                                                                                                                                | production<br>production<br>production<br>production<br>production               | 369<br>373<br>378<br>381<br>381               |  |  |  |  |

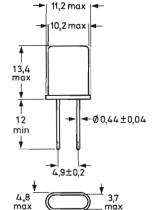

| 4322 143 04400<br>4322 143 04290                                                                         | quartz crystal (3,58 MHz)<br>idem (4,78 MHz)                                                                                                                                                                                    | production production                                                            | 385<br>385                                    |  |  |  |  |

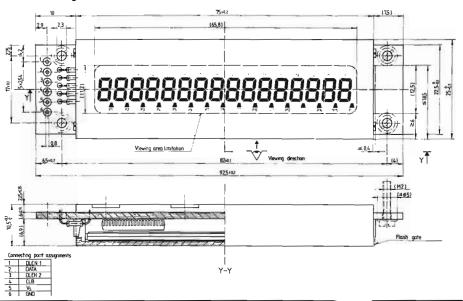

| MB7020160                                                                                                | 16 digit numeric LCD module                                                                                                                                                                                                     | production                                                                       | 387                                           |  |  |  |  |

|                                                                                                          | OTHER COMPONENTS FOR TELEPHONY                                                                                                                                                                                                  |                                                                                  |                                               |  |  |  |  |

|                                                                                                          | ISDN-kit<br>IST-bus interface circuit                                                                                                                                                                                           | development                                                                      | 395                                           |  |  |  |  |

BIPOLAR ICs FOR TELEPHONE SUBSCRIBER SETS

CMOS ICs FOR TELEPHONE SUBSCRIBER SETS

OTHER COMPONENTS FOR TELEPHONE SUBSCRIBER SETS

OTHER COMPONENTS FOR TELEPHONY

## DEDICATED INTEGRATED CIRCUITS FOR TELEPHONE SETS

#### Introduction

Over the past ten years advances in microcircuit technology have resulted in the development of microprocessors, memories, and dedicated ICs that are now beginning to replace the traditional components of the subscriber set, to the benefit of both its performance and appearance.

For example, ICs for interrupted current-loop dialling (decadic or pulse) and for dual-tone multi-frequency (DTMF) dialling allow the dial to be replaced by a push-button keyboard. And by replacing the carbon microphone with an active type (electret or electro-dynamic) and using an electronic anti-sidetone circuit, the speech and transmission functions can be performed by an IC. Speech and dialling functions can also be integrated onto a single chip. In addition, the bell will eventually be replaced by an electronically driven transducer with a variety of ringing tones.

Microcircuits also allow incorporation of a host of new features such as automatic redialling, repertory dialling, automatic emergency-call dialling, dialled number display, tariff-unit metering, speech synthesis, hands-free and cordless telephone operation, and possibly a limited amount of data handling.

Research is also progressing into developing an Integrated Services Digital Network (ISDN), in which digitized voice, circuit-switched data and digital signalling combined with packet switched data can be processed. This trend will lead to the development of ICs for interface and protocol functions (firstly in office communication systems, and eventually in the public network).

The long life of existing equipment and the fact that their manufacture is often automated, means that several years must elapse whilst new components prove their operational and economic superiority to the telephone authorities. Many of the new components will therefore have to work alongside the old ones, and the order and speed of approach to all-electronic subscriber equipment will not necessarily be the same in all countries. We have therefore produced, or are developing the wide range of microcircuits listed on page 1 for telephones of the present and future. We also offer a range of components for protection against lightning and mains contact, MOS transistors for current loop interruption, quartz crystals, loudspeakers and a complete LCD module. In addition, we are developing a wide range of components for the subscriber line card, and for the ISDN.

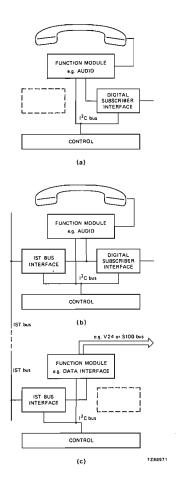

## ARCHITECTURE OF ELECTRONIC SUBSCRIBER SETS

The first step in converting subscriber sets to electronic operation will usually be replacement of the rotary dial by a pushbutton keyboard operating in conjunction with either a pulse generator for interrupted current-loop dialling or a tone generator for DTMF dialling. This effectively divides electronic telephone production into two main streams - one for sets with pulse dialling and one for sets with tone dialling. Subsequent steps are replacement of the carbon microphone by an active transducer such as an electret or electrodynamic microphone, and replacement of the transformer hybrid by an integrated speech/transmission circuit. The sequence continues with the inclusion of features such as repertory dialling, last-number redial, extended redial, dialled number display, and tariff-unit metering. There will also be some sets capable of either pulse or DTMF dialling.

The ringer is a completely separate function and can therefore be replaced by electronics at any stage.

## Telephones for pulse dialling

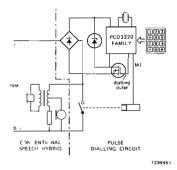

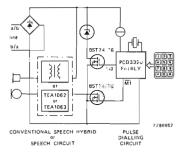

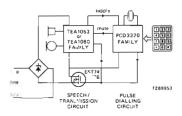

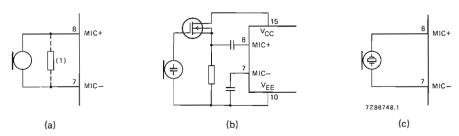

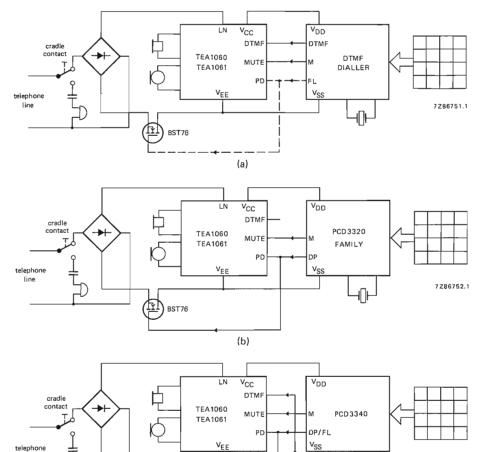

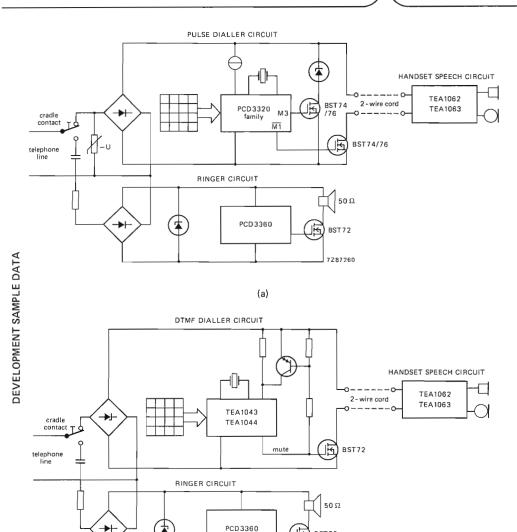

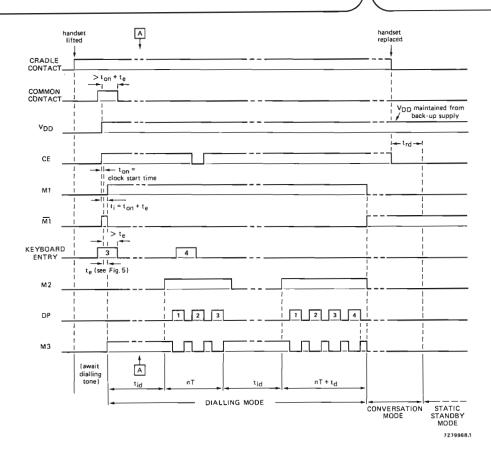

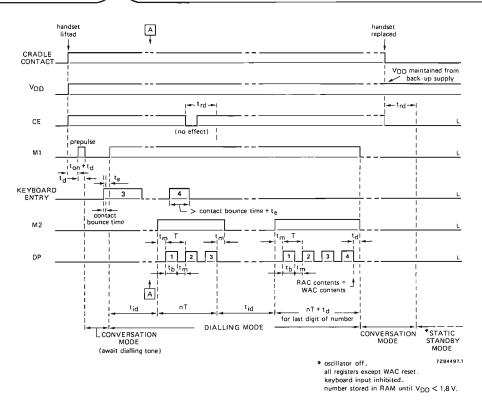

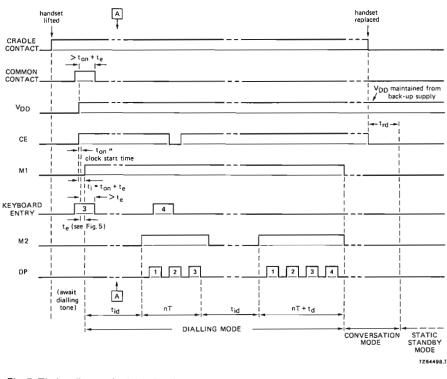

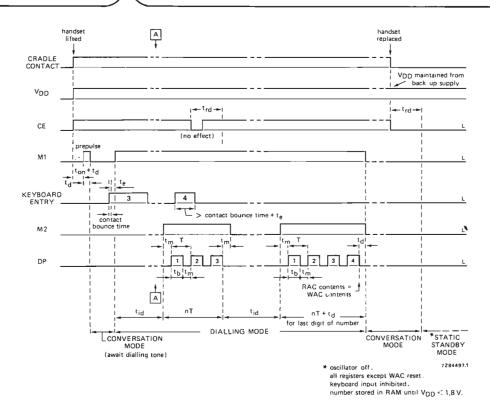

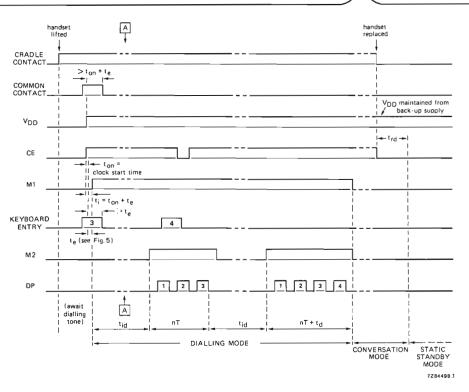

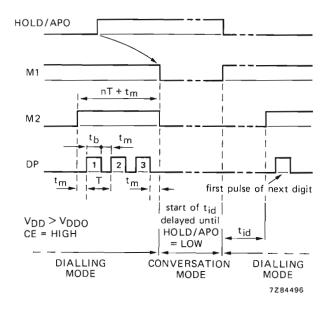

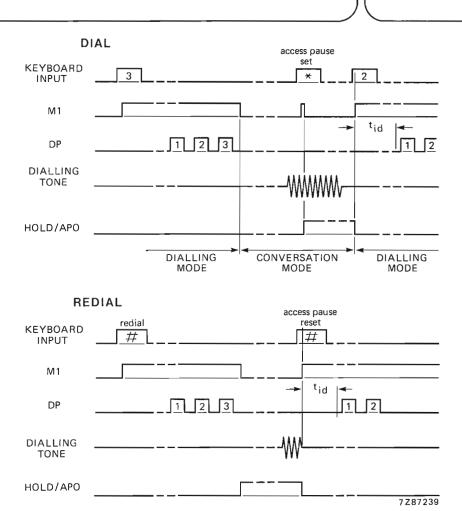

Fig. 1 opposite shows the architecture of three basic pushbutton subscriber sets for interrupted current-loop dialling using the PCD 3320 family of ICs.

Fig. 1a shows an insert unit to perform the dial function in a conventional set with a transformer hybrid. The muting relay inhibits the speech function during dialling.

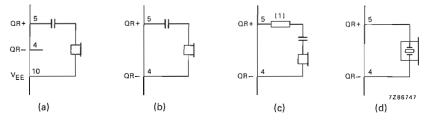

Fig. 1b shows a parallel circuit in which the line current flows through either the speech part or a dummy load, and is interrupted by the M3 output of the dialling IC. Note: the conventional speech circuit operating on two wires may be replaced by a speech circuit without electronic muting (TEA 1062/1063). This allows the possibility of operating the speech IC in the handset with only a two-wire cable.

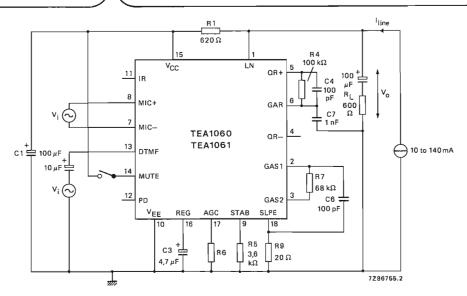

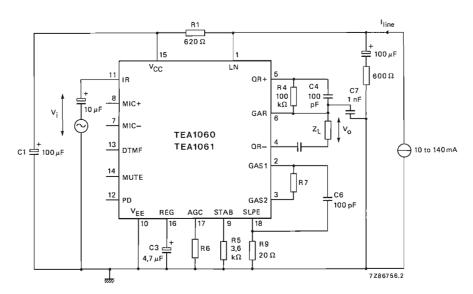

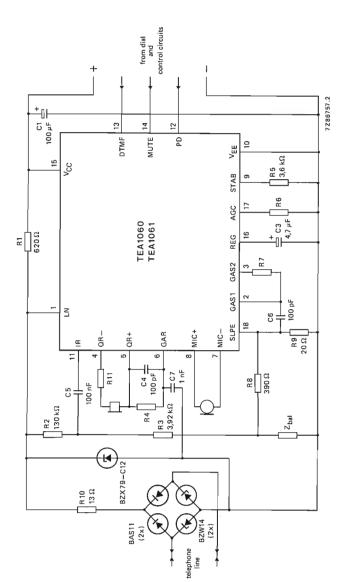

In Fig. 1c the dialling IC operates in conjunction with a transmission IC with common-line interface. The latter works with either an electret or an electrodynamic microphone and has a special input for muting. For this function we have a variety of speech/transmission ICs (TEA 1042, 1053, 1054, 1055, 1060 and 1061).

(a) Pulse dial insert unit replacing the rotary dial.

in a conventional telephone set.

(b) Pulse dial basic set with either conventional or electronic speech.

(c) Pulse dial basic set with two ICs and common line interface.

Fig.1 Subscriber set architecture for current loop interrupt dialling (excluding ringer, cradle contact, polarity guard & protection.

## Telephones for DTMF dialling

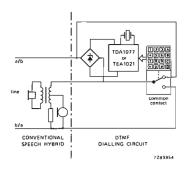

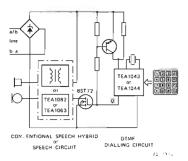

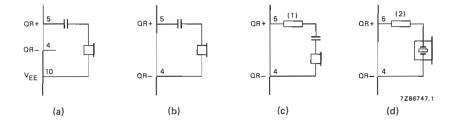

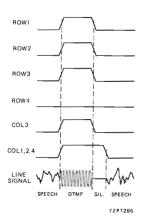

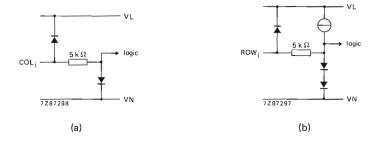

Fig. 2 shows the architecture of four basic pushbutton sets for DTMF dialling.

In Fig. 2a a DTMF insert replaces the rotary dial. This requires a DTMF generator with output stage and voltage stabilizer, e.g. the TEA 1077 or its improved successor the TEA 1021, both of which require a common contact to switch between speech and dialling.

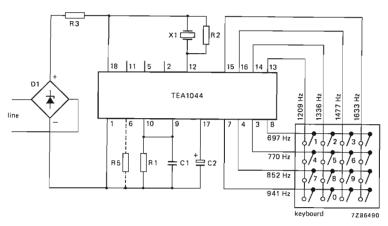

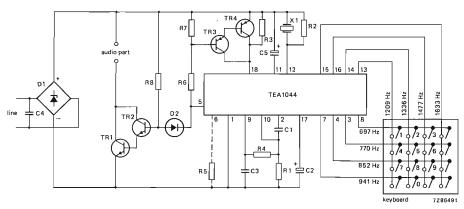

In Fig. 2b the electronic mute output of the TEA 1043/TEA 1044 enables electronic switching from dialling to speech, using a single-contact keyboard. As in Fig. 1b, electronic speech circuits like the TEA 1062 and 1063 may replace conventional ones.

In Fig. 2c a CMOS DTMF generator operates in conjunction with the speech/transmission circuit with electronic muting. This incorporates a voltage stabilizer and an audio output stage for both speech and DTMF signals. Note, the range of speech/transmission ICs referred to above in connection with Fig. 1c can also be used in this application.

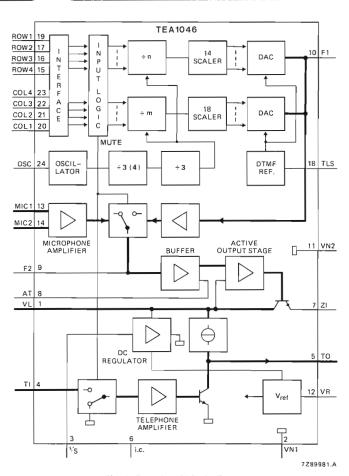

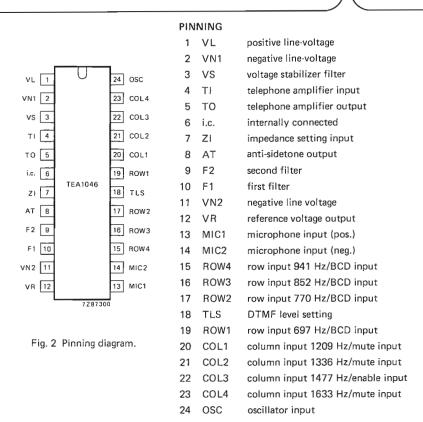

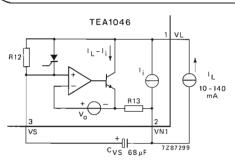

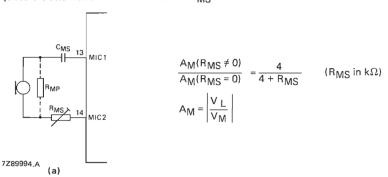

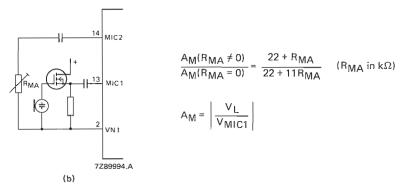

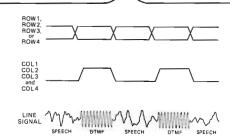

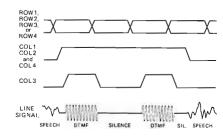

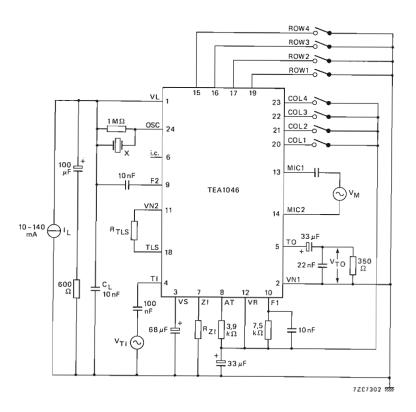

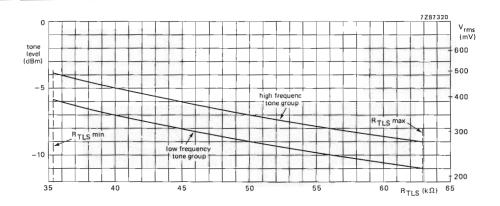

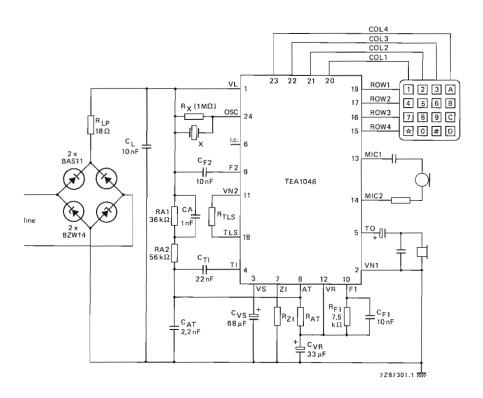

Fig. 2d shows the application of a combined DTMF/transmission circuit, the TEA 1046. Unlike the TEA 1042/53/54/55/60/61/62 and 63, the TEA 1046 has no line current controlled gain. It does, however, offer an economic solution for simple DTMF subscriber sets.

(a) DTMF insert unit replacing the rotary dial in a conventional telephone set.

(b) DTMF basic set with either conventional speech or electronic speech.

(c) DTMF basic set with two ICs and common line interface. (d) Electronic speech and DTMF on a single chip.

Fig.2 Subscriber-set architecture for dual-tone multi-frequency (DTMF) dialling (excluding ringer, cradle contact, polarity guard & protection).

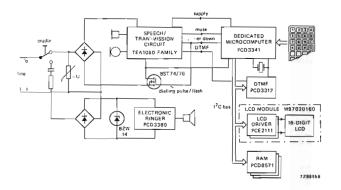

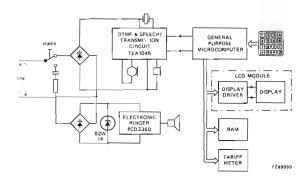

## Telephones with extended features

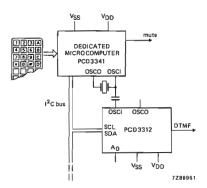

Fig. 3a shows a subscriber set with additional features such as last-number redial, extended redial, repertory dialling, register recall and dialled number display.

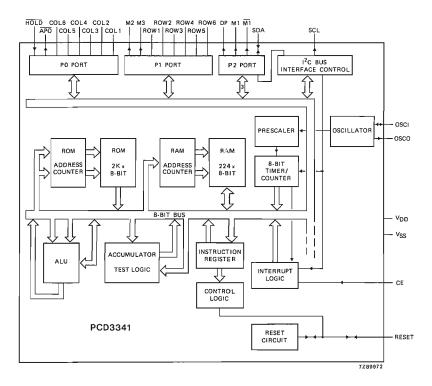

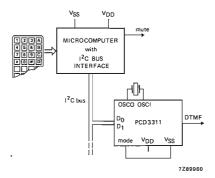

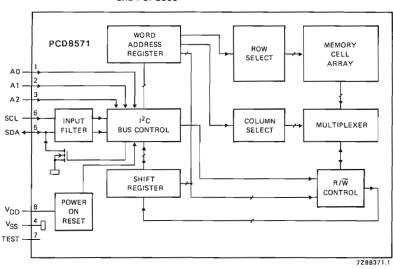

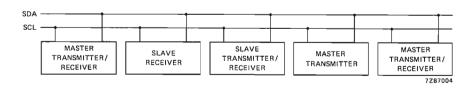

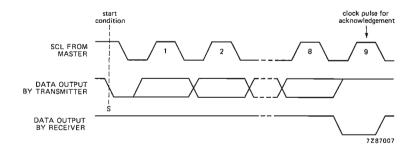

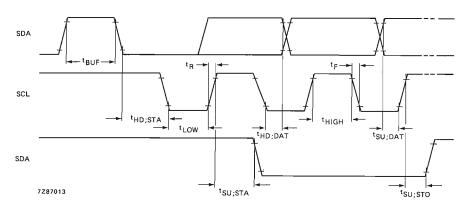

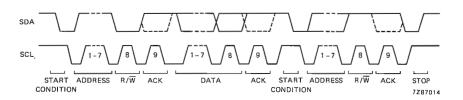

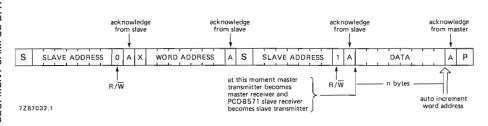

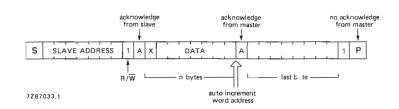

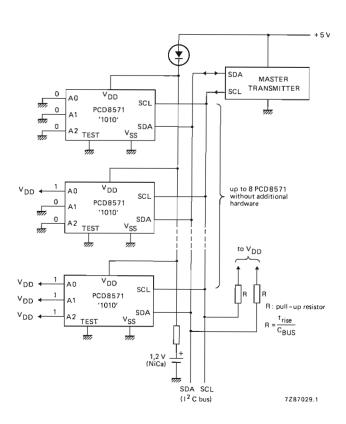

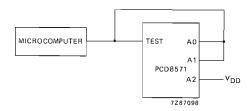

The PCD 3341 pulse repertory dialler/telephoneset-controller can store ten 16-digit numbers. It can also be augmented by connecting eight PCD 8571 CMOS RAMs to the |2C-bus (a two-wire serial I/O that can be used to connect peripherals to the PCD 3341). Besides the serial RAM, an LCD driver, a clock/ timer circuit and DTMF peripherals PCD 3312 and PCD 3311 are available (the latter intended to operate with 4 or 8 bit microcomputers with parallel interface).

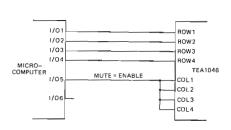

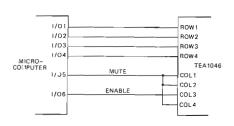

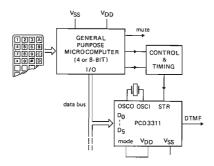

Fig. 3b shows a variation using a general-purpose microcomputer with parallel I/O in conjunction with the TEA 1046 DTMF/speech/transmission IC (which has microcomputer compatible keyboard inputs).

(a) Feature-phone using dedicated microcomputer PCD334-1.

(b) Variation using a generalpurpose microcomputer with parallel I/O.

Fig.3 Subscriber-set architecture with extended features.

# COMPARISONS

| Bipolar DTMF generators                                                                                                                                                                                           | TDA1077           |          | TEA1021    |          | TEA1043           |          | TEA1044    |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|------------|----------|-------------------|----------|------------|----------|

| I <sup>2</sup> L technology                                                                                                                                                                                       | •                 |          | •          |          | •                 |          | •          |          |

| on-chip line adaption                                                                                                                                                                                             | •                 |          | •          |          | •                 |          | •          |          |

| mute output                                                                                                                                                                                                       |                   |          |            |          | •                 |          | •          |          |

| adjustable dynamic impedance                                                                                                                                                                                      |                   |          |            |          |                   |          | •          |          |

| crystal oscillator frequency (MHz)                                                                                                                                                                                | 4,7               | 8        | 4,7        | 8        | 4,7               | 8        | 4,7        | 8        |

| min. line current (mA) max. or guaranteed typical                                                                                                                                                                 | 15<br>12          |          | 10<br>8    |          | 10<br>8           |          | 10<br>8    |          |

| number of pins                                                                                                                                                                                                    | 16                |          | 16         |          | 16                |          | 18         |          |

| external filter components<br>required to meet CEPT CS203<br>recommendation                                                                                                                                       | 2 R<br>2 C<br>L(1 |          | 2 F<br>3 C |          | 2 F<br>2 C<br>L ( |          | 2 F<br>3 C |          |

| Transmission ICs                                                                                                                                                                                                  | TEA 1042          | TEA 1053 | TEA 1054   | TEA 1055 | TEA 1060          | TEA 1061 | TEA 1062   | TEA 1063 |

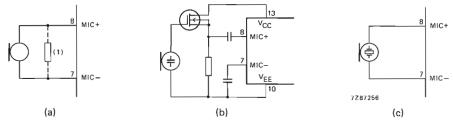

| microphone inputs low sensitivity — dynamic or magnetic medium sensitivity — dynamic or magnetic electret with source follower electret with preamplifier piezo-electric electret with preamplifier (loudspeaker) | •                 | •        | •          | •        | :                 | :        | :          | •        |

| receiver outputs dynamic or magnetic piezo-electric output for loudspeaker amplifier                                                                                                                              | •                 | •        | •          | •        | •                 | :        | :          | •        |

| mode switch handset/loudspeaker                                                                                                                                                                                   | •                 |          |            |          |                   |          |            |          |

| electronic mute input                                                                                                                                                                                             | •                 | •        | •          | •        | •                 | •        |            |          |

| DTMF input                                                                                                                                                                                                        | •                 | •        | •          | •        | •                 | •        |            |          |

| voltage regulator<br>adjustable d.c. voltage<br>adjustable d.c. resistance                                                                                                                                        | •                 | •        | •          | •        | •                 | •        | •          | •        |

| power down input                                                                                                                                                                                                  |                   |          |            |          | •                 | •        |            |          |

| gain control                                                                                                                                                                                                      |                   |          |            |          |                   |          |            |          |

| control to be switched off adapted to 400 $\Omega$ feed                                                                                                                                                           | •                 | •        | •          | •        | •                 | •        | •          | •        |

| adapted to 600 $\Omega$ feed                                                                                                                                                                                      | -                 |          | -          | -        | •                 | •        | •          | •        |

| adapted to 800 $\Omega$ feed adaptable to exchange sypply voltage                                                                                                                                                 | •                 | •        | •          | •        | •                 | •        | •          | •        |

## Pulse diallers with redial - PCD 3320 Family

|                                                                 | PCD3320 | PCD3321  | PCD3332 | PCD3323      | PCD3324  | PCD3325  |

|-----------------------------------------------------------------|---------|----------|---------|--------------|----------|----------|

| number of pins                                                  | 18      | 18       | 18      | 28           | 18       | 18       |

| dial-pulse frequencies (Hz)                                     | 10      | 10       | 10      | 10           | 10       | 10       |

| or<br>or                                                        |         | 16<br>20 |         | 16<br>20     | 16<br>20 | 16<br>20 |

| mark/space ratio                                                | 3/2     | 3/2      | 3/2     | 3/2          | 3/2      | 3/2      |

| or                                                              |         | 2/1      | 7, -    | 2/1          | 2/1      | 2/1      |

| interdigit pause duration (ms)                                  |         |          |         |              |          |          |

| @ 10 Hz dial-pulse frequency                                    | 790     | 790      | 790     | 790<br>888   | 790      | 790      |

| or<br>@ 16 Hz dial-pulse frequency<br>or                        |         | 515      |         | 515<br>579   | 515      | 515      |

| @ 20 Hz dial-pulse frequency or                                 |         | 412      |         | 412<br>463   | 412      | 412      |

| reset delay for line<br>power breaks (ms)                       |         |          |         |              |          |          |

| @ 10 Hz dial-pulse frequency or                                 | 158     | 158      | 158     | 158<br>316   | 158      | 158      |

| @ 16 Hz dial-pulse frequency or                                 |         | 103      |         | 103<br>206   | 103      | 103      |

| @ 20 Hz dial-pulse frequency or                                 |         | 82,4     |         | 82,4<br>165  | 82,4     | 82,4     |

| access-pause duration (s)                                       |         |          |         |              |          |          |

| @ 10 Hz dial-pulse frequency<br>or                              |         | 3,16     |         | 3,16<br>6,32 | 3,16     | 1)       |

| @ 16 Hz dial-pulse frequency<br>or                              |         | 2,06     |         | 2,06<br>4,12 | 2,06     | 1)       |

| @ 20 Hz dial-pulse frequency or                                 |         | 1,65     |         | 1,65<br>3,30 | 1,65     | 1)       |

| max. number of automatically-<br>inserted access pauses         | 0       | 2        | 0       | 2            | 1        | 0        |

| manually-insertable access pauses                               |         | •        |         | •            | •        | •        |

| I/Os                                                            |         |          |         |              |          |          |

| M1, mute output                                                 | •       | •        | •       | •            | •        | •        |

| M1, inverted output M2, strobe output                           | •       |          |         |              |          |          |

| M3, M1·DP                                                       | •       |          |         | •            |          |          |

| CL, clock output                                                |         | _        |         | •            | _        | _        |

| APO, access pause output <sup>2</sup> ) APR, access pause reset |         | •        |         |              | •        | •        |

| AAE, automatic access-pause                                     |         |          |         | •            |          |          |

| enable * key recognition                                        |         | •        |         |              |          | _        |

| * key recognition                                               |         | •        |         |              |          | _        |

terminated by access tone or via keyboard

connected to HOLD input in PCD 3321/3324/3325

BIPOLAR ICs FOR TELEPHONE SUBSCRIBER SETS

DTMF diallers with line interface

## TWO-TONE GENERATOR FOR TELEPHONE DIALLING

This integrated circuit is a tone generator, supplying frequency combinations (in accordance with CCITT recommendations) for use in push-button telephones.

The various frequencies are derived from a crystal-controlled oscillator followed by a sine-wave synthesizer. I<sup>2</sup> L technology is used, allowing the use of both digital and analogue functions. The built-in current/voltage regulator and output amplifier substantially reduce the number of external components. Only a quartz crystal of 4,783 MHz, a few resistors and capacitors are required. The circuit features:

- Stabilized working voltage.

- Frequency synthesizer.

- Adjustable output level.

- Output stage included.

- Two key roll-over provided.

- Keyboard inputs protected.

## QUICK REFERENCE DATA

| Working voltage               | V <sub>P</sub>  | typ. 3,3 V                   |  |

|-------------------------------|-----------------|------------------------------|--|

| Supply current range          | Ι <sub>Ρ</sub>  | 15 to 150 mA                 |  |

| Surge current (max. 100 μs)   | IS              | max. 850 mA                  |  |

| Low frequencies               | f               | 697, 770, 852 and 941 Hz     |  |

| High frequencies              | f               | 1209, 1336, 1477 and 1633 Hz |  |

| Operating ambient temperature | <sub>Tamb</sub> | −25 to +70 °C                |  |

| Storage temperature           | $T_{stg}$       | −55 to + 125 °C              |  |

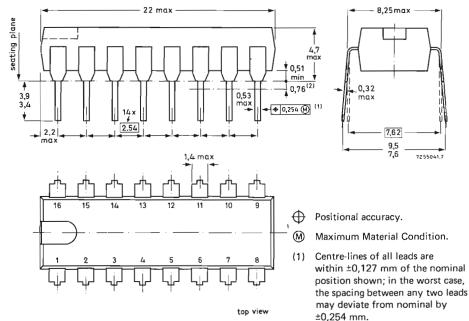

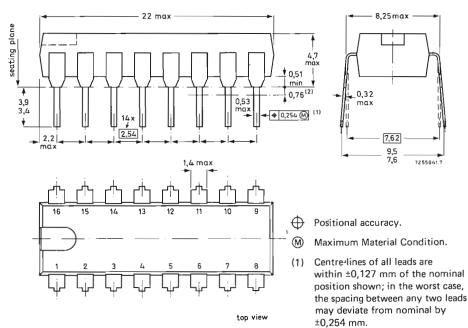

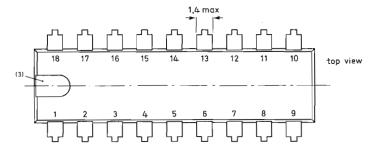

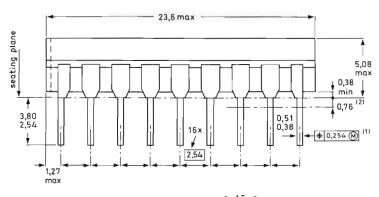

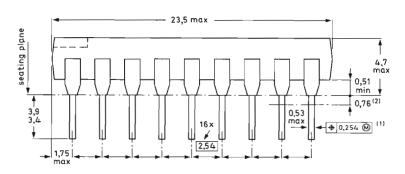

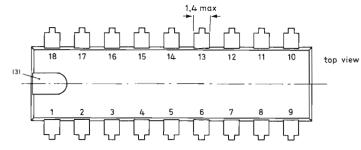

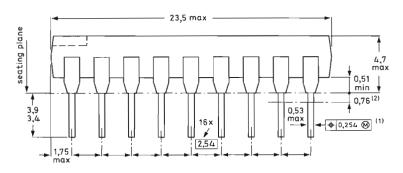

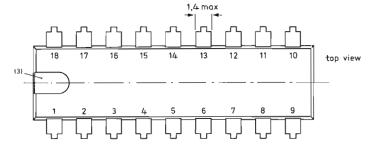

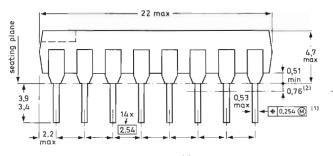

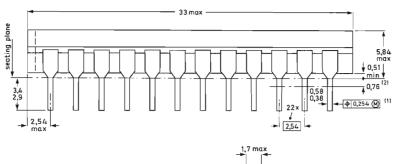

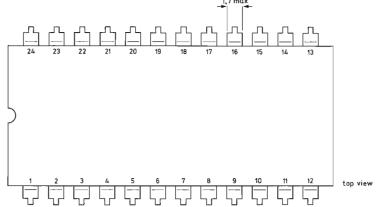

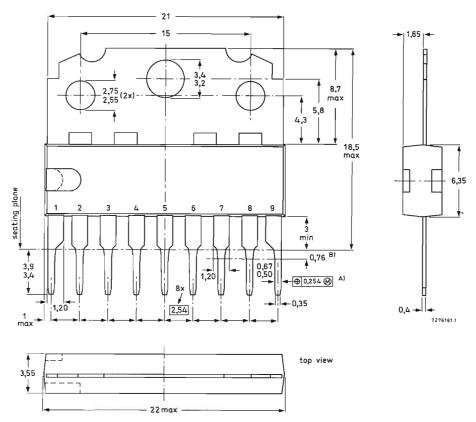

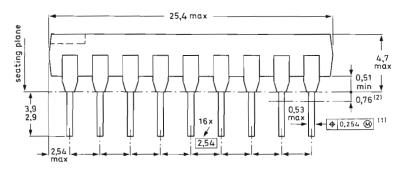

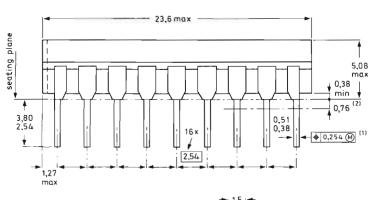

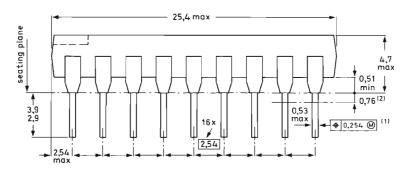

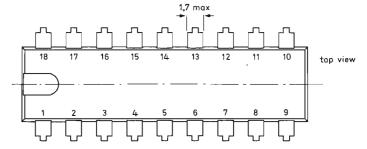

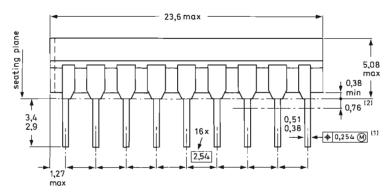

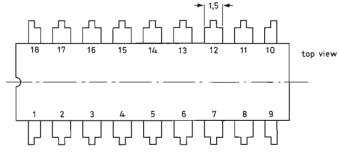

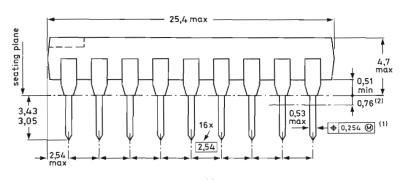

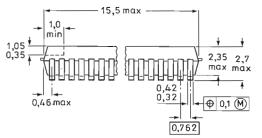

## PACKAGE OUTLINES

TDA1077P: 16-lead DIL; plastic (SOT-38). TDA1077D: 16-lead DIL; ceramic (SOT-74).

## **RATINGS**

| RATINGS                                                                            |                                       |             |                       |                     |

|------------------------------------------------------------------------------------|---------------------------------------|-------------|-----------------------|---------------------|

| Limiting values in accordance with the Absolute Maximum                            | System                                | (IEC 134)   |                       |                     |

| Input series resistance                                                            | $R_S$                                 | min.        | 33                    | Ω                   |

| Supply current                                                                     | lρ                                    | max.        | 150                   | mA                  |

| Surge current (max. 100 μs)                                                        | Is                                    | max.        | 850                   | mΑ                  |

| Operating ambient temperature                                                      | $T_{amb}$                             |             | -25 to +70            | oC                  |

| Storage temperature                                                                | $T_{stg}$                             |             | -55 to + 125          | °C                  |

| Junction temperature                                                               | Tj                                    | max.        | 125                   | oC                  |

| CHARACTERISTICS                                                                    |                                       |             |                       |                     |

| Working voltage (d.c.)<br>$I_O = 15 \text{ mA}$ ; $T_{amb} = 25 ^{\circ}\text{C}$  | V <sub>P</sub>                        | typ.        | 3,3<br>3,8            |                     |

| Supply current<br>TDA1077P                                                         | lр                                    |             | 15 to 80              | mA                  |

| TDA1077D                                                                           | lΡ                                    |             | 15 to 120             | mΑ                  |

| Low frequencies                                                                    | f                                     | 697, 7      | 70, 852 and 941       | Hz                  |

| High frequencies                                                                   | f                                     | 1209, 1336, | 1477 and 1633         | Hz                  |

| Frequency accuracy                                                                 |                                       | typ.        | 0,2<br>1,5            | %*<br>%             |

| Nominal output (adjustable by R3; see Figs 1 and 2)<br>Lower tones<br>Higher tones |                                       |             | -6 to −11<br>-4 to −9 |                     |

| Tolerance on total output level                                                    |                                       |             | ± 2                   | dB                  |

| Pre-emphasis                                                                       |                                       | typ.        | 1,2 to 2,5<br>2       | dB<br>dB ·          |

| Maximum total distortion with respect to total level                               | d <sub>tot</sub>                      | < <         | -24<br>-30            |                     |

| Unwanted signal levels < 3,4 kHz < 3,4 kHz > 50 kHz                                |                                       | typ.        | -40                   | dBm<br>dBm*<br>dBm* |

| Tone delay after actuation                                                         | <sup>t</sup> d                        | <           | 7                     | ms*                 |

| Switch bounce elimination                                                          | t <sub>sb</sub>                       | typ.        | 1                     | ms                  |

| Keyboard resistance<br>Contact "ON"<br>Contact "OFF"                               | R <sub>Kon</sub><br>R <sub>Koff</sub> | <<br>>      | 10<br>300             | kΩ<br>kΩ            |

|                                                                                    |                                       |             |                       |                     |

<sup>\*</sup> Values with recommended external components; see Figs 1 and 2.

## APPLICATION INFORMATION

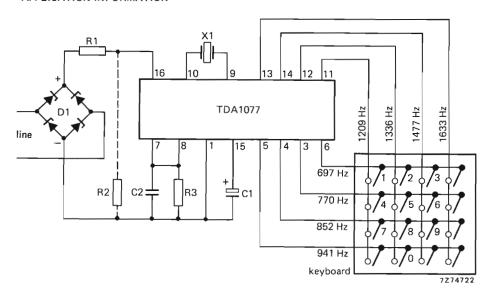

Fig. 1 Circuit diagram for telephone tone generator.

**PHILIPS**

Internal resistance R<sub>i</sub> = 900  $\Omega$  when R2 =  $\infty$ .

Internal resistance  $R_i = 600 \Omega$  when  $R2 = 1500 \Omega$ .

R3 adjusts tone output level; exact value depends on load impedance and required output level.

## Components

| R1 metal film resistor MR25 5%      | $33 \Omega$          |

|-------------------------------------|----------------------|

| R2 metal film resistor MR25 5%      | 1500 Ω               |

| R3 metal film resistor MR24         | $pprox$ 2 k $\Omega$ |

| C1 solid AI. electrolytic 6,3 V     | 4,7 μF               |

| C2 met. pol. film cap. 10% (nugget) | 27 nF                |

| D1 transient suppressor bridge      | BZW10                |

| X1 quartz crystal                   | 4,783 MHz            |

## APPLICATION INFORMATION (continued)

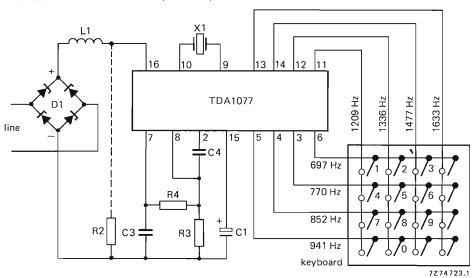

Fig. 2 Circuit diagram for telephone tone generators including C.I.S.P.R. requirements. Low harmonic distortion (—80 dBm at 50 kHz).

## Components

| R2 metal film resistor MR25 5% | $1500 \Omega$          | C1 solid A1. electrolytic 6,3 V    | 4,7 μF    |

|--------------------------------|------------------------|------------------------------------|-----------|

| R3 metal film resistor MR24    | $\approx$ 2 k $\Omega$ | C3 miniature ceramic plate cap. 2% | 10 nF     |

| R4 metal film resistor MR24 1% | 4,7 k $\Omega$         | C4 met. pol. film cap. 10%         | 33 nF     |

| L1 coil (33 Ω)                 | 15 mH                  | D1 transient suppressor bridge     | BZW10     |

|                                |                        | X1 quartz crystal                  | 4,783 MHz |

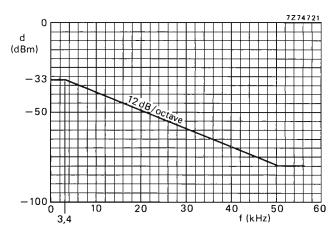

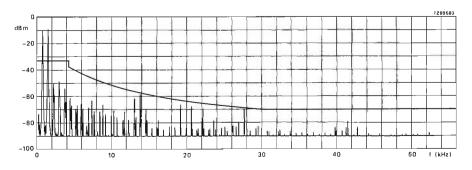

Fig. 3 Harmonic distortion.

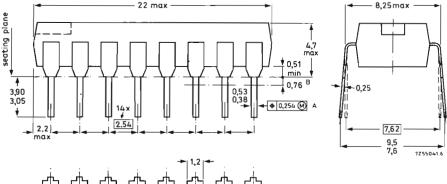

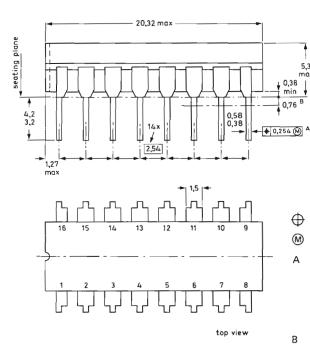

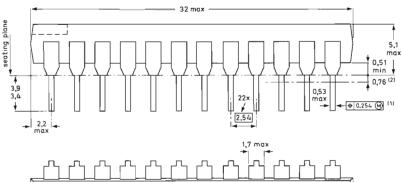

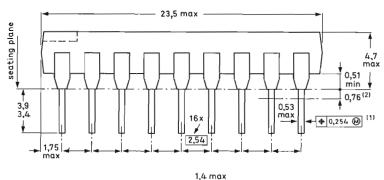

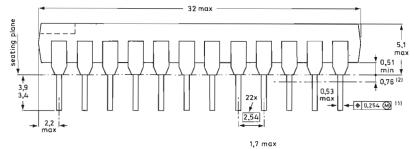

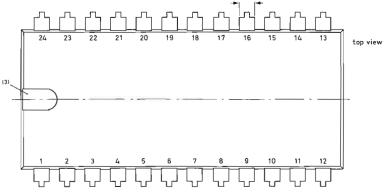

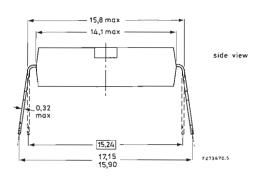

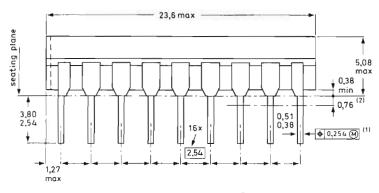

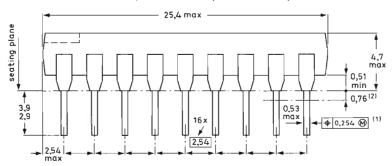

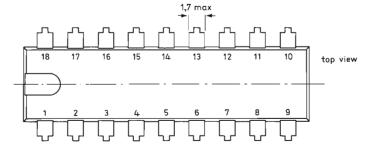

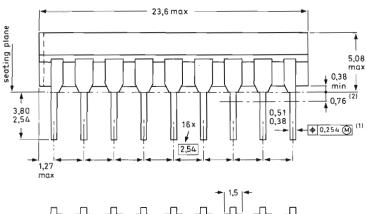

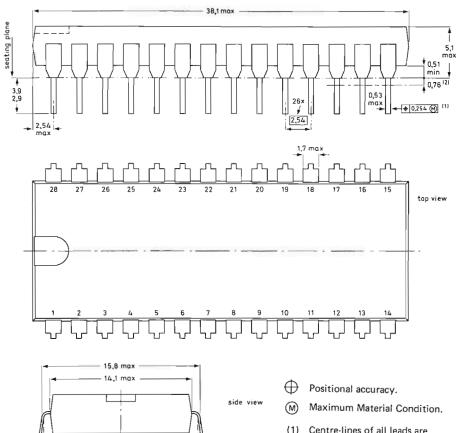

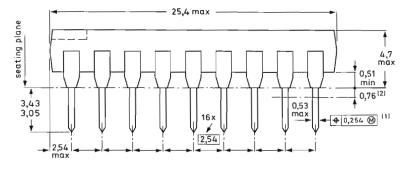

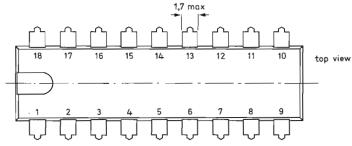

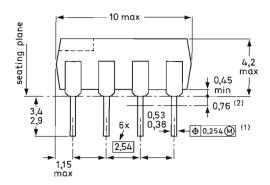

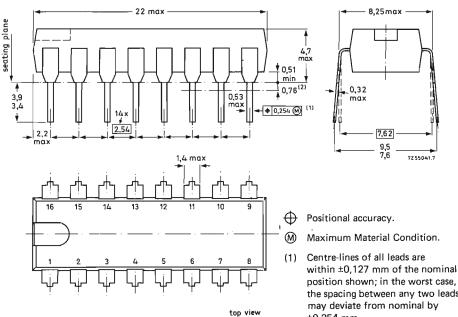

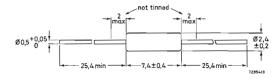

## 16-LEAD DUAL IN-LINE; PLASTIC (SOT-38)

top view

Dimensions in mm

Positional accuracy.

- (M) Maximum Material Condition.

- A Centre-lines of all leads are within ±0,127 mm of the nominal position shown; in the worst case, the spacing between any two leads may deviate from nominal by ±0,254 mm.

- B Lead spacing tolerances apply from seating plane to the line indicated.

## SOLDERING

## 1. By hand

Apply the soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300  $^{\circ}$ C it must not be in contact for more than 10 seconds; if between 300  $^{\circ}$ C and 400  $^{\circ}$ C, for not more than 5 seconds.

## 2. By dip or wave

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

## 3. Repairing soldered joints

The same precautions and limits apply as in (1) above.

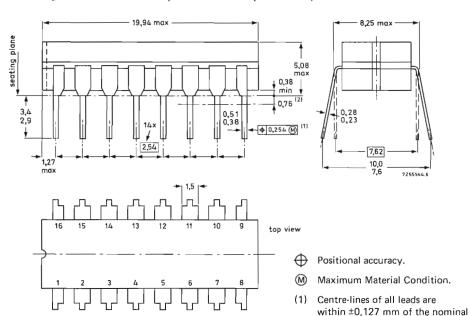

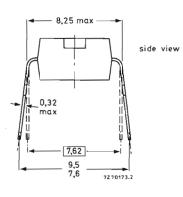

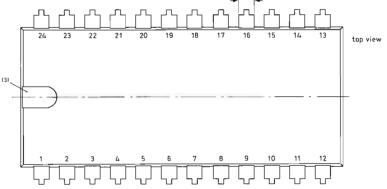

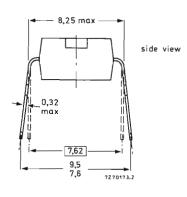

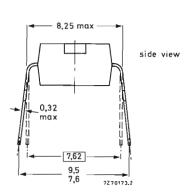

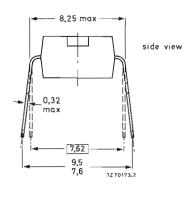

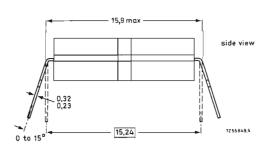

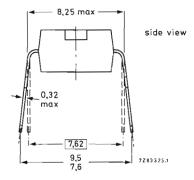

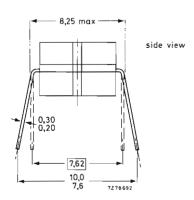

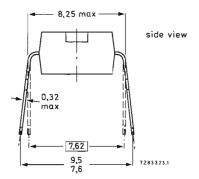

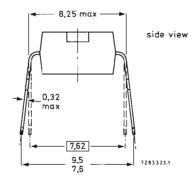

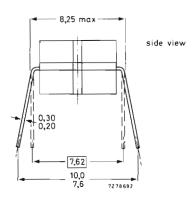

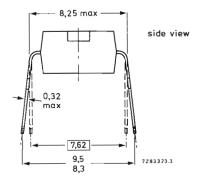

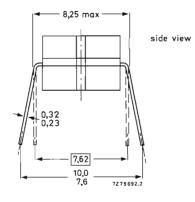

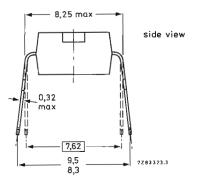

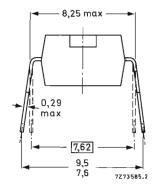

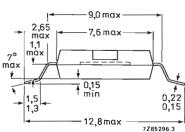

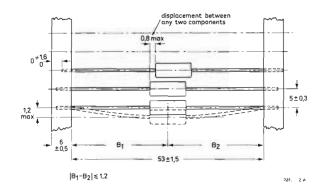

# 16-LEAD DUAL IN-LINE; CERAMIC (SOT-74)

5,3 max

Positional accuracy.

0,25

Maximum Material Condition.

8,25 max

7,62 10,0 7,6

7255544.4

- Centre-lines of all leads are within ±0,127 mm of the nominal position shown; in the worst case, the spacing between any two leads may deviate from nominal by ±0,254 mm.

- В Lead spacing tolerances apply from seating plane to the line indicated.

Dimensions in mm

## Remarks

- 1. Leads are given positive misalignment so that they grip after insertion.

- 2. Leads are Ni-Fe, pure tin plated.

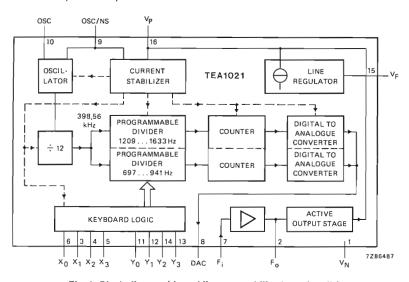

## DTMF GENERATOR FOR TELEPHONE DIALLING

This integrated circuit is a dual-tone multi-frequency (DTMF) generator, supplying frequency combinations (in accordance with CCITT recommendations) for use in pushbutton telephones, with a common contact on the keyboard for muting.

The various frequencies are derived from a crystal-controlled oscillator followed by a sinewave synthesizer.

I<sup>2</sup>L technology allows digital and analogue functions to be implemented on the same chip. The built-in current/voltage regulator and active output amplifier substantially reduce the number of external components. Only a quartz crystal of 4,78 MHz and a few resistors and capacitors are required.

#### The circuit features:

- wide operating line current range

- operating voltage down to 1,3 volt

- no individual tone level adjustment required

- temperature stabilized signal levels

- line current independent signal levels

- output stage and line regulator included

- all pins protected against electrostatic discharges

- two key roll-over provided

- operates with a low cost quartz crystal

- few external components required

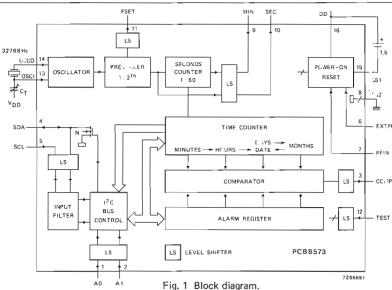

Fig. 1 Block diagram (dotted lines are stabilized supply rails).

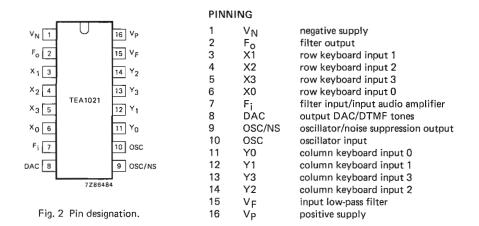

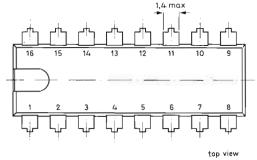

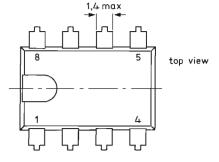

## PACKAGE OUTLINES

TEA1021P: 16-lead DIL, plastic (SOT-38). TEA1021D: 16-lead DIL, ceramic (SOT-74B).

## **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply current                       | Ι <sub>Ρ</sub>   | max.                | 150   | mΑ |

|--------------------------------------|------------------|---------------------|-------|----|

| Surge current ( $t_p$ < 250 $\mu$ s) | IS               | max.                | 850   | mΑ |

| Input series resistance              | $R_s$            | min.                | 18    | Ω  |

| Operating ambient temperature range  | $T_{amb}$        | -25 to              | + 70  | oC |

| Storage temperature range            | T <sub>stg</sub> | -55 to <sup>-</sup> | + 125 | oC |

| Junction temperature                 | Ti               | max.                | 125   | oC |

## CHARACTERISTICS

$V_N = 0 V$ ;  $T_{amb} = -25 \text{ to } + 70 \text{ }^{\circ}\text{C}$  unless otherwise specified.

|                                                          | symbol                                                                   | min.                  | typ.                         | max.        | unit                 | conditions                                     |

|----------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|------------------------------|-------------|----------------------|------------------------------------------------|

| operating voltage<br>d.c.; -IL = 10 mA                   | ٧L                                                                       | 2,8                   | 3,3                          | 3,8         | v                    |                                                |

| line current<br>level — 7 dBm<br>level — 2 dBm           | IL<br>IL                                                                 | 10<br>12              | 8<br>9                       | 120<br>120  | mA<br>mA             |                                                |

| internal impedance                                       | Zi                                                                       | 640                   | 900                          | 1150        | Ω                    | 300 – 3400 Hz                                  |

| tone frequencies                                         |                                                                          |                       |                              |             |                      |                                                |

| low                                                      | f <sub>x0</sub><br>f <sub>x1</sub><br>f <sub>x2</sub><br>f <sub>x3</sub> | <br>  -<br>  -<br>  - | 697<br>770<br>852<br>941     | <br><br>-   | Hz<br>Hz<br>Hz<br>Hz | frequency                                      |

| high                                                     | fy0<br>fy1<br>fy2<br>fy3                                                 |                       | 1209<br>1336<br>1477<br>1633 | -<br>-<br>- | Hz<br>Hz<br>Hz<br>Hz | 4 782 720 Hz                                   |

| dividing error                                           | '                                                                        | _                     | _                            | 0,11        | %                    | '                                              |

| nom, output level<br>lower frequency<br>higher frequency | V <sub>LG</sub><br>V <sub>HG</sub>                                       | <u>-</u>              | -                            | -6<br>-4    | dBm<br>dBm           | adjustable<br>adjustable                       |

| tolerance<br>on output level                             | ΔVο                                                                      | 2                     | _                            | 2           | dB                   |                                                |

| pre-emphasis                                             |                                                                          | 1,3                   | 2                            | 2,7         | dB                   | without filter components                      |

| distortion with respect to total level                   | d <sub>tot</sub>                                                         | _                     | -34                          | -24         | dВ                   | maximum tone level and with first-order filter |

| start up time                                            | t <sub>s</sub>                                                           | _                     | 5                            | _           | ms                   | with recommended external components           |

| switch bounce<br>elimination                             | t <sub>sb</sub>                                                          | 1                     | 1,5                          | 2           | ms                   | ·                                              |

| required keyboard resistance                             |                                                                          |                       |                              |             |                      |                                                |

| contact on contact off                                   | R <sub>k</sub> on                                                        | -<br>500              |                              | 10<br>      | kΩ<br>kΩ             |                                                |

**PHILIPS**

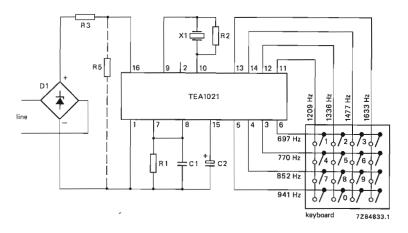

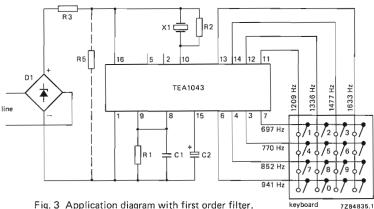

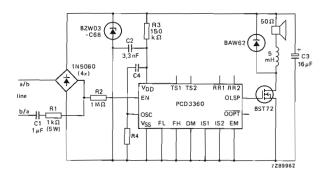

Fig. 3 Application diagram with first-order filter.

| R1<br>R2<br>R3<br>R5 | metal film resistor<br>metal film resistor<br>metal film resistor<br>metal film resistor            | MR16<br>SFR16<br>SFR16<br>SFR16 | 1%<br>5%<br>5%<br>5% | see Fig. 7 3,3 M $\Omega$ 18 $\Omega$ 2700 $\Omega$ (for Z $_{\rm O}$ = 600 $\Omega$ ; |

|----------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|----------------------|----------------------------------------------------------------------------------------|

| C1<br>C2<br>D1       | metallized polyester film capacitor<br>solid aluminium electrolytic capacitor<br>polarity guard and |                                 | 6,3 V                | no resistor for $Z_0$ = 900 $\Omega$ ) see Fig. 7 4,7 $\mu$ F                          |

| X1                   | transient suppressor bridge (see Fig. 6) quartz crystal                                             |                                 |                      | 2 x BAS11 and 2 x BZW03<br>4,783 MHz                                                   |

**PHILIPS**

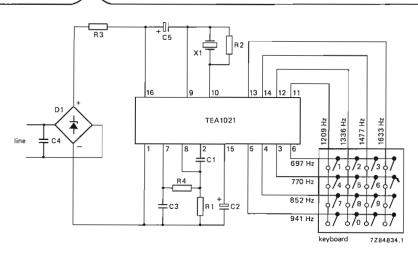

Fig. 4 Application diagram with second-order filter to minimize harmonic distortion (meets CEPT CS203 requirements).

| R1 | metal film resistor                      | MR16  | 1%    | see Fig. 7                            |

|----|------------------------------------------|-------|-------|---------------------------------------|

| R2 | metal film resistor                      | SFR16 | 5%    | 3,3 MΩ                                |

| R3 | metal film resistor                      | SFR16 | 5%    | 18 Ω                                  |

| R4 | metal film resistor                      | SFR16 | 5%    | 270 kΩ                                |

| C1 | metallized polyester film capacitor      |       |       | see Fig. 7                            |

| C2 | solid aluminium electrolytic capacitor   |       | 6,3 V | 4,7 μF                                |

| C3 | miniature ceramic plate capacitor        |       |       | 180 pF                                |

| C4 | metallized polyester film capacitor      |       |       | 22 nF                                 |

| C5 | solid aluminium electrolytic capacitor   |       | 6,3 V | 4,7 μF                                |

| D1 | transient suppressor bridge (see Fig. 6) |       |       | $2 \times BAS11$ and $2 \times BZW03$ |

| X1 | quartz crystal                           |       |       | 4,783 MHz                             |

|    |                                          |       |       |                                       |

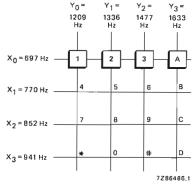

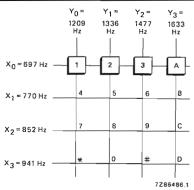

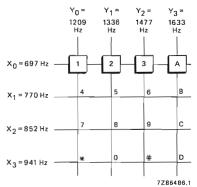

Fig. 5 Allocation of dialling tones to keyboard functions.

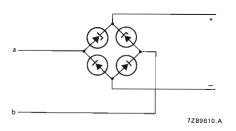

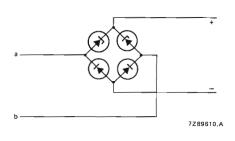

Fig. 6 Polarity-guard and line-transient suppression bridge D1.

Diodes 2 x BAS11.

Voltage regulators 2 x BZW03-..

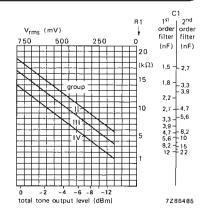

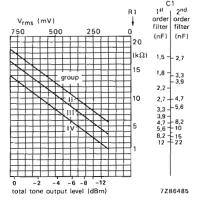

Fig. 7 Level adjustment (see Figs 3 and 4).

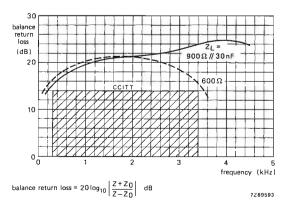

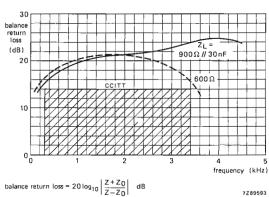

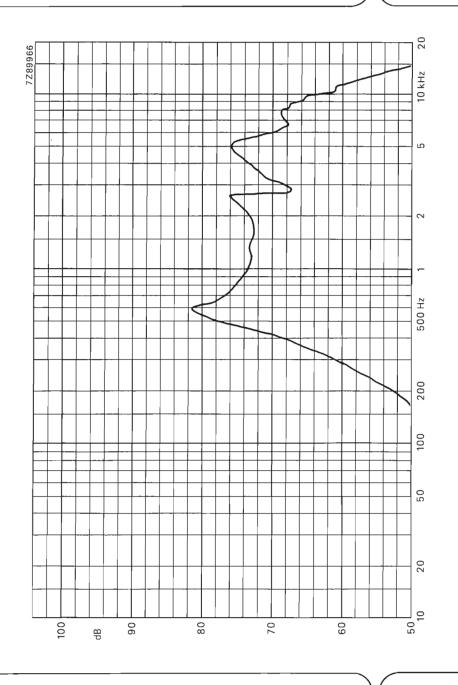

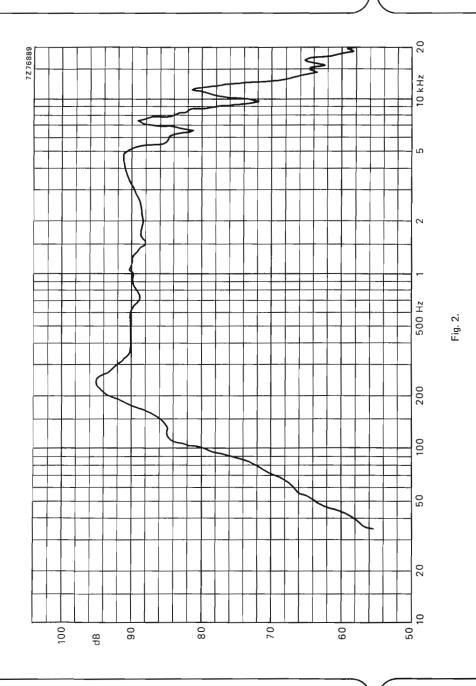

Fig. 8 Balance return loss measured with external components as in Fig. 4.

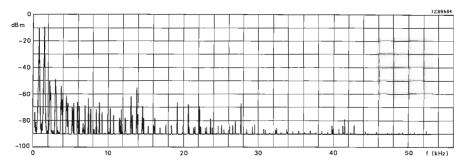

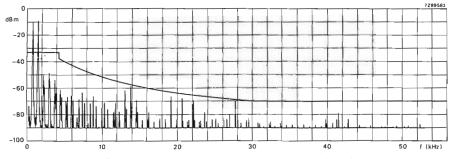

Fig. 9 Frequency spectrum of circuit with second-order filter (see Fig. 4).

## APPLICATION (see Fig. 4)

## Line matching

If there is an impedance match between the lines and the dialling circuit, the balance return loss will be high and reflections on the line will be highly damped. Figure 8 shows that the balance return loss when using the application diagram as shown in Fig. 4 is more than 14 dB. The variation of balance return loss with the frequency is largely caused by an impedance variation due to the low-pass filter capacitor (C2) and the radio-frequency interference filter capacitor C4. Since the highest line impedance that is likely to be encountered is  $900~\Omega$  the internal impedance of the dialling circuit is set at this level and can be reduced to match lower impedance lines by adding an external resistor between pins 1 and 16. If direct current must be eliminated a capacitor must be connected in series with the resistor.

- internal impedance  $Z_i = 900 \Omega$ ; no external resistor between pins 1 and 16.

- internal impedance  $Z_i$  = 600  $\Omega$ ; external resistor between pins 1 and 16 = 2700  $\Omega$ .

## Output level adjustment

The tone output levels are subject to some spread due to manufacturing tolerances and can be adjusted by selection of the value of the resistor connected to pin 8.

The level of the higher-frequency tone however is always  $2\pm0.7$  dB above that of the lower-frequency tone. The total production of the circuits is therefore divided into groups. The group to which any of the integrated circuits belongs is identified by dots on the body of the circuit, the number of dots corresponding with the group number. The combined tone output level is shown as a function of resistor value with group number as a parameter in Fig. 7. After the resistor value has been selected to obtain the required tone output level, the value of the filter capacitor connected to the same pin must be determined. For passive first-order filters (Fig. 4) the time-constant (RC) must be  $26~\mu s$ . For active second-order filters it must be  $46~\mu s$ . These values accommodate the different attenuation levels for the various tone frequencies due to the 0.3 dB hump at the breakpoint of the filters.

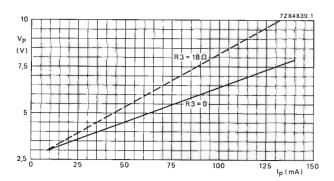

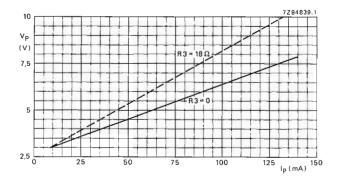

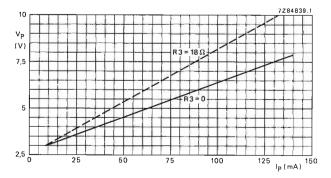

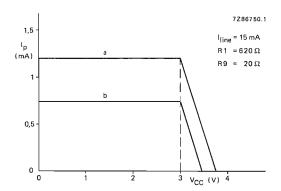

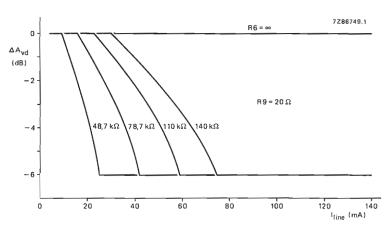

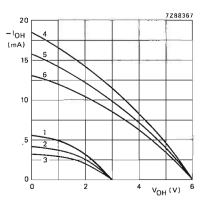

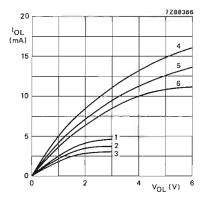

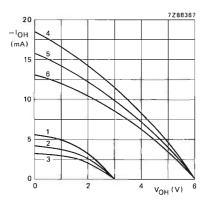

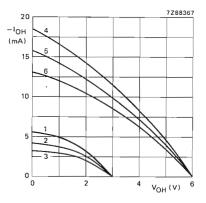

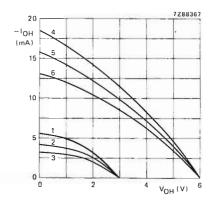

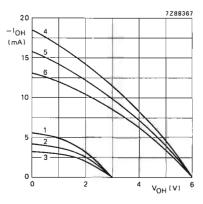

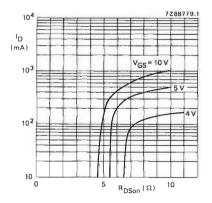

Fig. 10 D.C. characteristics.

7755041.7

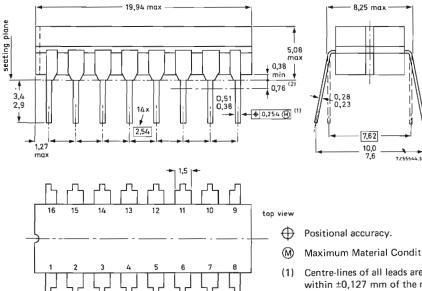

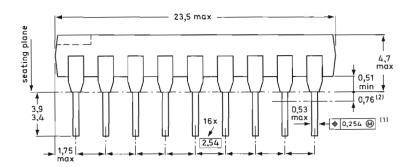

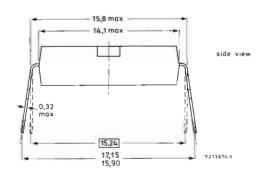

# 16-LEAD DUAL IN-LINE; PLASTIC (SOT-38)

Dimensions in mm

(2) Lead spacing tolerances apply from seating plane to the line

indicated.

## SOLDERING

#### 1. By hand

Apply the soldering iron below the seating plane (or not more than 2 mm above it). If its temperature is below 300 °C it must not be in contact for more than 10 seconds; if between 300 °C and 400 °C, for not more than 5 seconds.

## 2. By dip or wave

The maximum permissible temperature of the solder is 260 °C; this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified storage maximum. If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

## 3. Repairing soldered joints

The same precautions and limits apply as in (1) above.

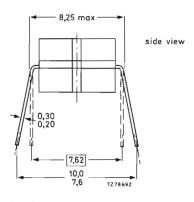

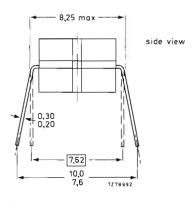

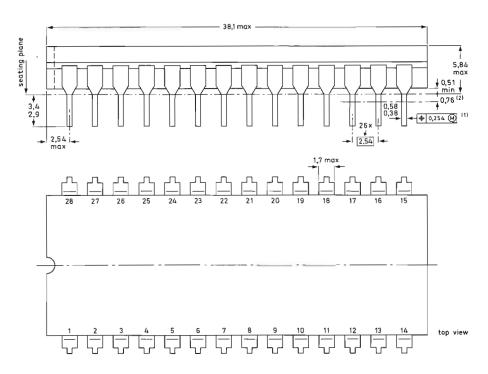

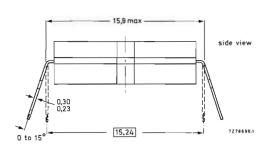

# 16-LEAD DUAL IN-LINE; CERAMIC (SOT-74)

## Dimensions in mm

## Lead spacing tolerances apply from seating plane to the line indicated.

±0,254 mm.

position shown; in the worst case, the spacing between any two leads may deviate from nominal by

## Remarks

- 1. Leads are given positive misalignment so that they grip after insertion.

- 2. Leads are Ni-Fe, pure tin plated.

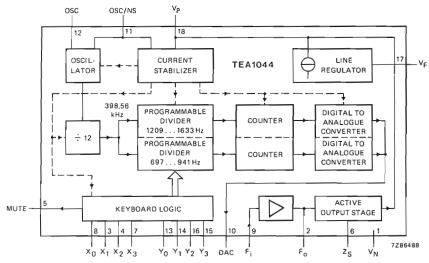

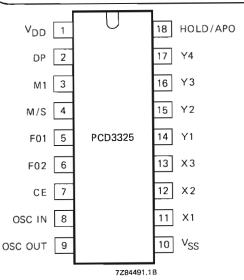

## DTMF GENERATOR FOR TELEPHONE DIALLING

This integrated circuit is a dual-tone multi-frequency (DTMF) generator, supplying frequency combinations (in accordance with CCITT recommendations) for use in pushbutton telephones, with a single contact keyboard.

The various frequencies are derived from a crystal-controlled oscillator followed by a sinewave synthesizer.

I<sup>2</sup> L technology allows digital and analogue functions to be implemented on the same chip. The built in current/voltage regulator and active output amplifier substantially reduce the number of external components. Only a quartz crystal of 4,78 MHz and a few resistors and capacitors are required.

## The circuit features:

- wide operating line current range

- operating voltage down to 1,3 volt (standby 0,7 volt)

- no individual tone level adjustment required

- temperature stabilized signal levels

- line current independent signal levels

- output stage and line regulator included

- all pins protected against electrostatic discharges

- two key roll-over provided

- operates with a low cost quartz crystal

- few external components required

- electronic mute facility

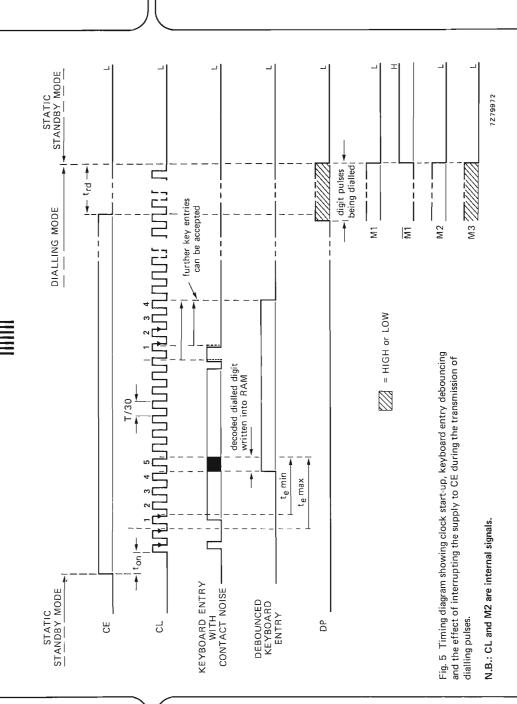

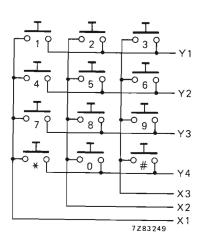

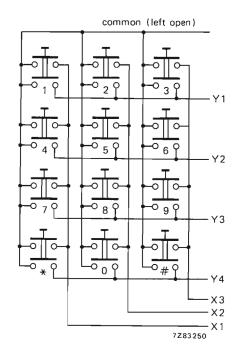

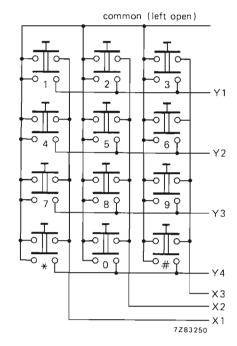

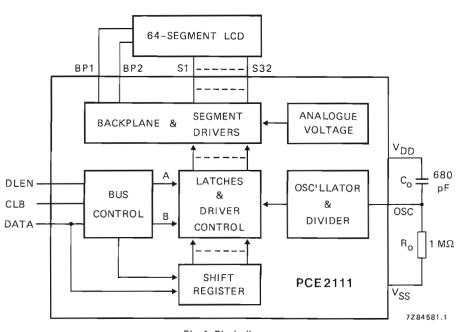

- low power consumption in standby mode 16 CURRENT OSCIL-LINE 15 TEA1043 LATOR REGULATOR STABILIZER 398 56 PROGRAMMABLE DIGITAL TO kHz DIVIDER COUNTER ANALOGUE 1209 . . . 1633 Hz CONVERTER PROGRAMMABLE DIGITAL TO ANALOGUE DIVIDER COUNTER 697 ... 941 Hz CONVERTER ACTIVE MUTE -KEYBOARD LOGIC **OUTPUT STAGE** 3 11 12 14 13 4

Y0 Y1 Y2 Y3

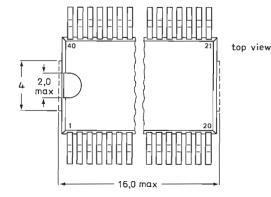

## PACKAGE OUTLINES

TEA1043P: 16-lead DIL, plastic (SOT-38). TEA1043D: 16-lead DIL, ceramic (SOT-74B).

X<sub>0</sub> X<sub>1</sub> X<sub>2</sub> X<sub>3</sub>

Fig. 1 Block diagram (dotted lines are stabilized supply rails).

7Z86489

## RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

150 mA lρ max. Supply current 850 mA Surge current (tp < 250  $\mu$ s) ۱s max. 18 Ω  $R_s$ min. Input series resistance -25 to +70 °C  $\mathsf{T}_{\mathsf{amb}}$ Operating ambient temperature range -55 to +125 °C Storage temperature range  $T_{sta}$ 125 °C  $T_i$ max. Junction temperature

## CHARACTERISTICS

$V_N$  = 0 V;  $T_{amb}$  = -25 to +70 °C unless otherwise specified.

|                                                                | symbol                                                                                      | min.             | typ.                             | max.             | unit                 | conditions                                     |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------|----------------------------------|------------------|----------------------|------------------------------------------------|

| operating voltage<br>d.c.; —I _ = 10 mA                        | V <sub>L</sub>                                                                              | 2,8              | 3,3                              | 3,8              | v                    | •                                              |

| line current<br>level — 7 dBm<br>level — 2 dBm<br>standby mode | <br>  <br>  <br>                                                                            | 10<br>12<br>–    | 8<br>9<br>50                     | 120<br>120<br>–  | mA<br>mA<br>μA       |                                                |

| internal impedance                                             | z <sub>i</sub>                                                                              | 640              | 900                              | 1150             | Ω                    | 300 — 3400 Hz                                  |

| tone frequencies<br>low<br>high                                | f <sub>x0</sub><br>f <sub>x1</sub><br>f <sub>x2</sub><br>f <sub>x3</sub><br>f <sub>y0</sub> | -<br>-<br>-<br>- | 697<br>770<br>852<br>941<br>1209 | _<br>_<br>_<br>_ | Hz<br>Hz<br>Hz<br>Hz | frequency<br>  quartz crystal 4 782 720 Hz     |

|                                                                | f <sub>y</sub> 1<br>f <sub>y</sub> 2<br>f <sub>y</sub> 3                                    | -<br>  -<br>  -  | 1336<br>1477<br>1633             | <u>-</u><br>-    | Hz<br>Hz<br>Hz       |                                                |

| dividing error                                                 |                                                                                             | _                | _                                | 0,11             | %                    |                                                |

| nom. output level<br>lower freq.<br>higher freq.               | V <sub>LG</sub><br>V <sub>HG</sub>                                                          | _<br>_           |                                  | -6<br>-4         | dBm<br>dBm           | adjustable<br>adjustable                       |

| tolerance on output level                                      | ΔV <sub>o</sub>                                                                             | 2                | _                                | 2                | dB                   |                                                |

| pre-emphasis                                                   |                                                                                             | 1,3              | 2                                | 2,7              | dB                   | without filter components                      |

| distortion with respect to total level                         | d <sub>tot</sub>                                                                            | _                | -34                              | -24              | dB                   | maximum tone level and with first-order filter |

| start up time                                                  | t <sub>S</sub>                                                                              | _                | 5                                | -                | ms                   | with recommended external components           |

| mute output sink current                                       | IMS                                                                                         | _                |                                  | 0,5              | mA                   |                                                |

| switch bounce elimination<br>required keyboard<br>resistance   | t <sub>sb</sub>                                                                             | 1                | 1,5                              | 2                | ms                   |                                                |

| contact on contact off                                         | R <sub>k off</sub>                                                                          | _<br>500         | _                                | 10<br>-          | kΩ                   |                                                |

**PHILIPS**

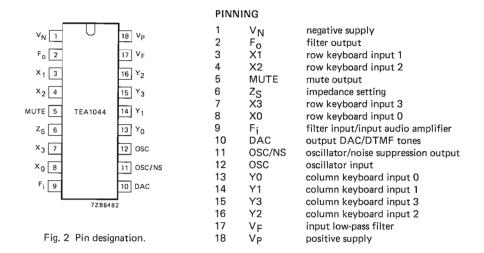

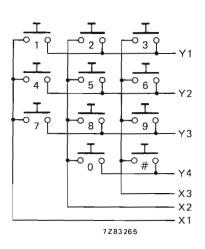

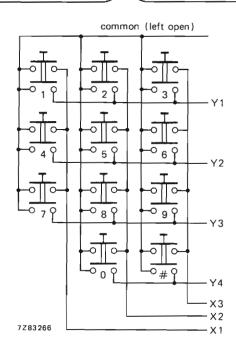

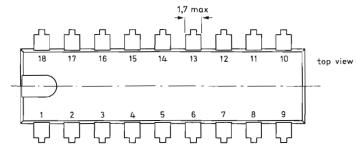

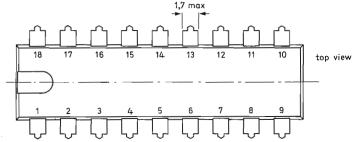

Fig. 2 Pin designation.

#### PINNING

| 1 | $V_N$ | negative supply |

|---|-------|-----------------|

| 2 | Fo    | filter output   |

|   |       |                 |

3 X1 row keyboard input 1 4 X2 row keyboard input 2

5 MUTE mute output

6 Х3 row keyboard input 3 7 X0 row keyboard input 0 8 Fi filter input/input audio amplifier

9 DAC output DAC/DTMF tones

10 OSC oscillator input 11 Y0 column keyboard input 0

column keyboard input 1 12 Y1 13 Y3 column keyboard input 3

14 Y2 column keyboard input 2 15 V<sub>F</sub> input low-pass filter

16 V<sub>P</sub> positive supply

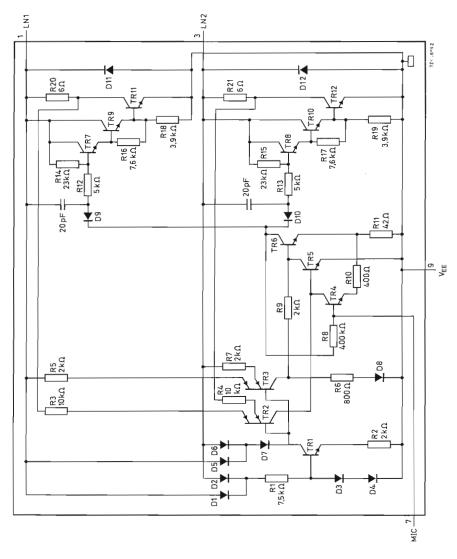

Fig. 3 Application diagram with first order filter.

| R1 | metal film resistor                     | MR16  | 1%    | see Fig. 7                                     |

|----|-----------------------------------------|-------|-------|------------------------------------------------|

| R2 | metal film resistor                     | SFR16 | 5%    | 3,3 MΩ                                         |

| R3 | metal film resistor                     | SFR16 | 5%    | 18 Ω                                           |

| R5 | metal film resistor                     | SFR16 | 5%    | 2700 $\Omega$ (for $Z_{\Omega} = 600 \Omega$ ; |

|    |                                         |       |       | no resistor for $Z_{\Omega} = 900 \Omega$ )    |

| C1 | metallized polyester film capacitor     |       |       | see Fig. 7                                     |

| C2 | solid aluminium electrolytic capacitors | i     | 6,3 V | 4,7 μF                                         |

| D1 | polarity guard and transient suppressor |       |       |                                                |

|    | bridge (see Fig. 6)                     |       |       | 2 x BAS11 and 2 x BZW03                        |

| X1 | quartz crystal                          |       |       | 4, 783 MHz                                     |

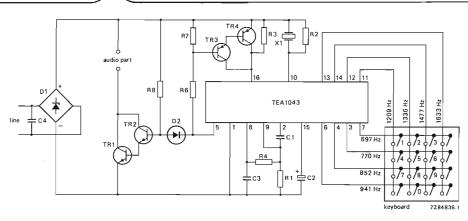

Fig. 4 Application diagram with electronic mute switch and second-order filter.

| R1  | metal film resistor                      | MR16      | 1%          | see Fig. 7                       |

|-----|------------------------------------------|-----------|-------------|----------------------------------|

| R2  | metal film resistor                      | SFR16     | 5%          | 3,3 ΜΩ                           |

| R3  | metal film resistor                      | SFR16     | 5%          | 39 kΩ (depends on audio voltage) |

| R4  | metal film resistor                      | SFR16     | 5%          | 270 kΩ                           |

| R6  | metal film resistor                      | SFR16     | 5%          | 330 kΩ                           |

| R7  | metal film resistor                      | SFR16     | 5%          | 820 kΩ                           |

| R8  | metal film resistor                      | SFR16     | 5%          | 470 kΩ                           |

| C1  | metallized polyester film capacitor      |           |             | see Fig. 7                       |

| C2  | solid aluminium electrolytic capacitor   |           | 6,3 V       | 4,7 μF                           |

| C3  | miniature ceramic plate capacitor        |           |             | 180 pF                           |

| C4  | metallized polyester film capacitor      |           |             | 22 nF                            |

| D1  | transient suppressor bridge (see Fig. 6) | 2 x BAS11 | and 2 x BZV | N03                              |

| D2  | diode                                    | BAW62     |             |                                  |

| TR1 | transistor                               | BC338     |             |                                  |

| TR2 | transistor                               | BC548     |             |                                  |

| TR3 | transistor                               | BC558     |             |                                  |

| TR4 | transistor                               | BC328     |             |                                  |

| X1  | quartz crystal                           |           |             | 4,783 MHz                        |

If TR1/TR2 = BSR50 and TR3/TR4 = BSR60 then R6 = 39 k $\Omega$ , R7 = 120 k $\Omega$  and R8 = 33 k $\Omega$ .

An additional choke of 15 mH in series with the circuit is required to meet the CEPT CS203 distortion requirements.

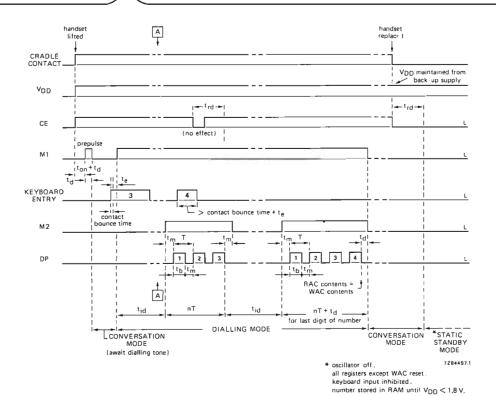

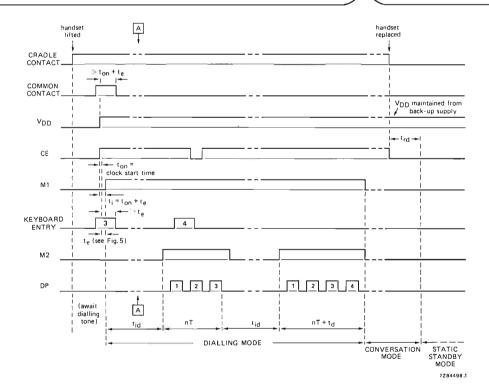

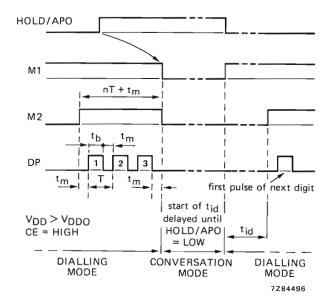

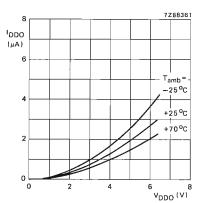

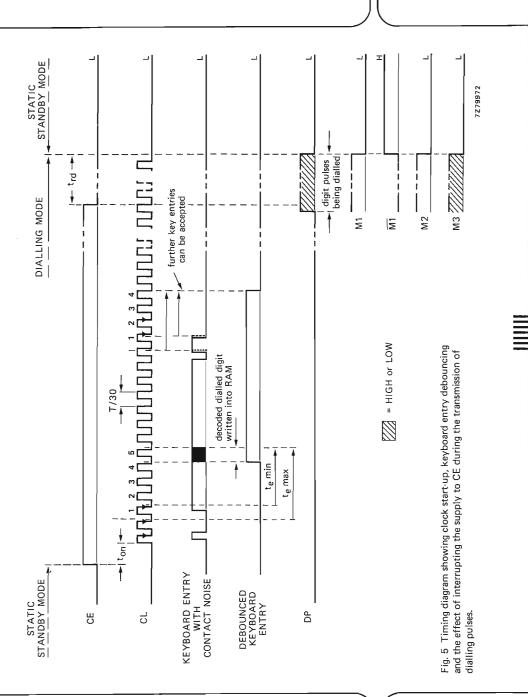

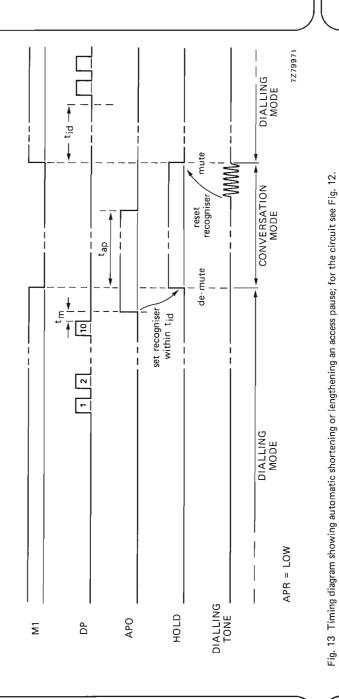

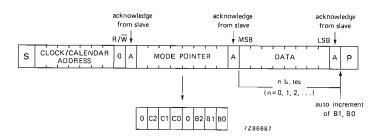

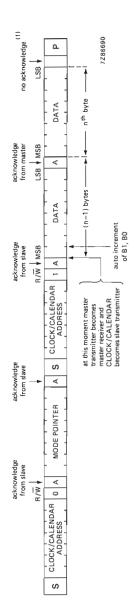

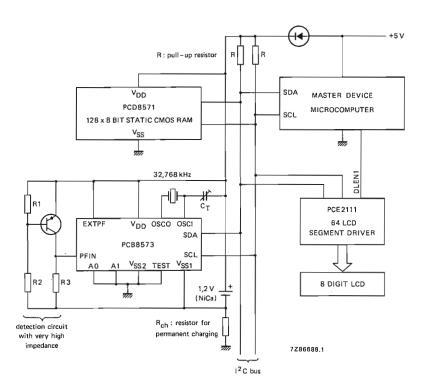

7289593